# Northumbria Research Link

Citation: Chiang, Ming-Feng (2009) High speed all-optical packet switching router employing single and multiple PPM based routing tables. Doctoral thesis, Northumbria University.

This version was downloaded from Northumbria Research Link: https://nrl.northumbria.ac.uk/id/eprint/2384/

Northumbria University has developed Northumbria Research Link (NRL) to enable users to access the University's research output. Copyright © and moral rights for items on NRL are retained by the individual author(s) and/or other copyright owners. Single copies of full items can be reproduced, displayed or performed, and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided the authors, title and full bibliographic details are given, as well as a hyperlink and/or URL to the original metadata page. The content must not be changed in any way. Full items must not be sold commercially in any format or medium without formal permission of the copyright holder. The full policy is available online: <a href="http://nrl.northumbria.ac.uk/policies.html">http://nrl.northumbria.ac.uk/policies.html</a>

# Northumbria Research Link

Citation: Chiang, Ming-Feng (2009) High speed all-optical packet switching router employing single and multiple PPM based routing tables. Doctoral thesis, Northumbria University.

This version was downloaded from Northumbria Research Link: http://nrl.northumbria.ac.uk/id/eprint/2384/

Northumbria University has developed Northumbria Research Link (NRL) to enable users to access the University's research output. Copyright © and moral rights for items on NRL are retained by the individual author(s) and/or other copyright owners. Single copies of full items can be reproduced, displayed or performed, and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided the authors, title and full bibliographic details are given, as well as a hyperlink and/or URL to the original metadata page. The content must not be changed in any way. Full items must not be sold commercially in any format or medium without formal permission of the copyright holder. The full policy is available online: <a href="http://nrl.northumbria.ac.uk/policies.html">http://nrl.northumbria.ac.uk/policies.html</a>

# High Speed All-optical Packet Switching Router Employing Single and Multiple PPM Based Routing Tables

# Ming-Feng Chiang

A thesis submitted for fulfilment of the requirements of Northumbria University for the degree of Doctor of Philosophy

Research undertaken in the School of Computing, Engineering and Information Sciences

October 2008

## **ABSTRACT**

All-optical packet switched networks with flexibility and capability to deal with the bursty traffic is one solution to deal with the ever increasing demand for bandwidth. To fully utilise the potential of such networks and to ensure that high-speed packets. passed through a number of nodes, are faithfully delivered to their intended destination with minimum delay times, packet header processing and routing decision needs to be carried out in the optical domain not in the electrical domain. This is to avoid the speed bottleneck imposed by the slow response of currently available electronic devices beyond 40 Gb/s. At present, packet header recognition is carried out by sequentially correlating the incoming packet header address with every entry of a local routing table. For a small size network, with a reasonable size routing table, sequential correlation is viable both in terms of processing speed and implementation complexity. However, for a large size network with a very large size routing table of hundreds or thousands of entries, the cost, complexity and processing time does become a real issue. The latter will lead to a noticeable increase in the packet processing time at every router, which could be significantly reduced by a nonconventional signal formatting. In this thesis, an all-optical 3-input AND gate and an all-optical 1×2 switch with high contrast ratio are proposed as an essential element in all-optical routers. New routing schemes employing pulse position modulation (PPM) packet header format as well as single and multiple PPM based routing tables (PPRTs) are proposed and investigated. The main advantage of the proposed scheme is reduced size routing table leading to a faster router processing time compared to the routers with conventional routing tables (CRTs). The correlation-time gains offered by the proposed schemes are given by theoretical calculations. For optical packets with 4-bit

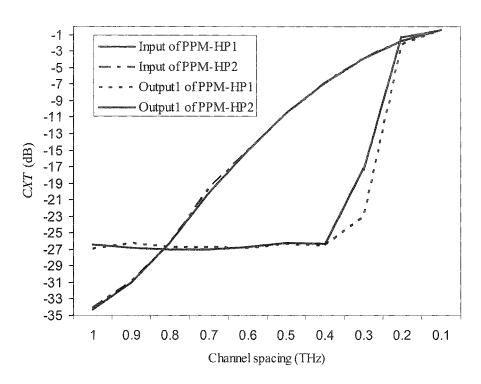

binary address, all-optical 1×3 routers employing single and multiple PPRTs with an entry slot of 6.25 ps offer ~ 100 and ~ 400 times faster processing times when compared to the routers employing CRT, respectively. The performance of the proposed routers employing single and multiple PPRTs are assessed in terms of optical signal-to-noise ratio (OSNR) in multi-hop routing by means of numerical simulations and theoretical analysis. It is shown that predicted and simulated OSNR decreases by ~2 dB after each hop. New packet header address formats proposed offers reduced complexity of nodes by employing single or multiple PPM based routing tables. Adopting a hybrid header address format, it is shown that routers with multiple PPRTs can operate at 160 Gb/s with the output intra-channel crosstalk of -18 dB and with output packet power fluctuation of 2 dB. Finally, a WDM router employing a single PPRT, capable of processing packets at different wavelengths simultaneously, is proposed and its inter-channel crosstalk performance is investigated. At 160 Gb/s, results obtained show an inter-channel crosstalk of ~ -27 dB at a channel spacing of greater than 0.4 THz and a demultiplexer bandwidth of 500 GHz.

## **ACKNOWLEDGEMENTS**

First of all, I would like to express my sincere gratitude to my principle supervisor Professor Z. Ghassemlooy for his continuous patience, guidance and inspiration throughout my research. Secondly, I would like to thank my second supervisor Dr. Wai Pang Ng. for his encouragement, support and those opportunities he provided to me. I couldn't have done it without their help and guidance.

I would also like to thank Dr. Hoa Le Minh, Mr. Wisit Loedhammacakra, Dr. Mark Leach and Dr. David Johnston for their help and useful discussions all the time. The past three years working in Northumbria Communication Research Lab with my colleagues Udu Ogah, Michael J. Fdo, Amiri Maryam, Wasiu Popoola, Sujan Rajbhandari, Ahmed Shalaby, Rupak Kharel, Yuan Yuan Jiang, Qing Lu, Mutsam Jarajreh, and Xuan Tang has been a great time and experience in my life.

Moreover, I would like to express the utmost gratitude to my parents Pi-Ching, Chiang and Mei-Yu, Lo, my brother Ming-Lun, Chiang and his wife to be Hsi-Chia, Chen for their endless love and encouragement to me. Besides, I would like to thank my girlfriend Chieh-Ju, Li for her unchanging love, understanding and support in the past three years, thanks for being there for me. I also want to thank her mother Hsueh-Chih, Hsing and sister Han-Ju, Li for their encouragement and support. They are the main driving force to keep my research study. Finally, I would like to dedicate this thesis to my grandmother Kui-Nu, Chiang-Chen who passed away on 06 February 2008 in Taipei, Taiwan. It was my regret I couldn't see her for the last time. She will always live in my memory.

# **DECLARATION**

I hereby declare that this thesis is entirely my own work and has not been submitted in support of an application of another degree or qualification of this or any other university, institute of learning or industrial organisation

Signature:

Name: Ming-Feng, Chiang

Date: 24 October 2008

# TABLE OF CONTENTS

| ABSTRACT                                                                  | .ii |

|---------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                          | iv  |

| DECLARATION                                                               | . ₩ |

| TABLE OF CONTENTS                                                         | vi  |

| GLOSSARY OF ACRONYMS                                                      | . X |

| GLOSSARY OF SYMBOLSx                                                      | iv  |

| LIST OF FIGURESxx                                                         | /ii |

| LIST OF TABLESx                                                           | хi  |

| CHAPTER 1 INTRODUCTION                                                    | .1  |

| 1.1 Background                                                            | . 1 |

| 1.2 Aims and Objectives                                                   | .6  |

| 1.3 Chapter Outline                                                       | .7  |

| 1.4 Original Contribution                                                 | .9  |

| CHAPTER 2 LITERATURE REVIEW OF ALL-OPTICAL ROUTIN                         | G   |

| SCHEMES AND ALL-OPTICAL SWITCHES                                          | 14  |

| 2.1 Introduction                                                          | 14  |

| 2.2 Evolution of Optical Network                                          | 15  |

| 2.3 Optical Network Topologies                                            | 18  |

| 2.4 All-optical Packet Switching Core Router and Header Recognition Schem | e.  |

|                                                                           | 23  |

| 2.4.1 All-optical packet switching core-router                            | 23  |

| 2.4.2 Packet header and header recognition                                | 26  |

| 2.5 All-optical Switches                                                  | 28  |

| 2.6 Ultrafast All-optical Switches                                        | 29  |

|     | 2.6.1   | Ultrafast nonlinear interferometer (UNI)                 | 30    |

|-----|---------|----------------------------------------------------------|-------|

|     | 2.6.2   | Terahertz optical asymmetric demultiplexing (TOAD)       | 31    |

|     | 2.6.3   | Mach-Zehnder interferometer (MZI)                        | 32    |

| 2.7 | Sur     | nmary                                                    | 34    |

| СН  | APTER 3 | 3SEMICONDUCTOR AMPLIFIER, SYMMETRIC                      | MACH- |

| ZE) | HNDER . | AND ITS APPLICATIONS                                     | 35    |

| 3.1 | Intr    | roduction                                                | 35    |

| 3.2 | Ser     | niconductor Optical Amplifier                            | 36    |

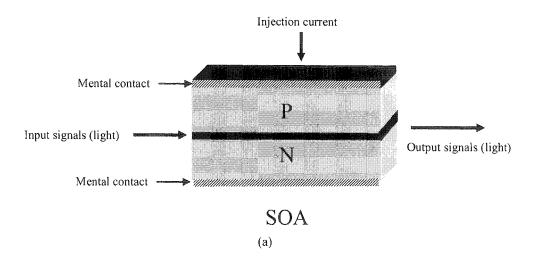

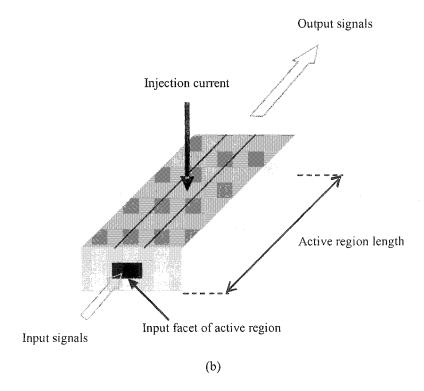

|     | 3.2.1   | SOA principle                                            | 37    |

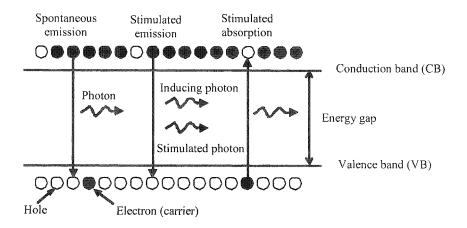

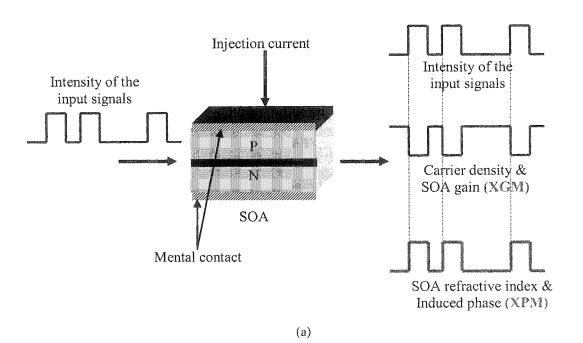

|     | 3.2.2   | SOA nonlinearities                                       | 39    |

| 3.3 | Syr     | nmetric Mach-Zehnder Switch                              | 41    |

| 3.4 | All     | -Optical Serial-to-Parallel Converter (SPC) Based on SMZ | 43    |

| 3.5 | All     | -Optical Logic Gates Based on SMZ                        | 53    |

| 3.6 | Hig     | gh Contrast Ratio 1×2 All-optical Switch Based on SMZ    | 60    |

| 3.7 | Thi     | ree-input AND Gate Based on FWM using a Single SOA       | 68    |

| 3.8 | Sur     | nmary                                                    | 75    |

| СН  | APTER 4 | 4 PPM BASED PACKET HEADER ADDRESS FORMAT                 | ſ77   |

| 4.1 | Inti    | roduction                                                | 77    |

| 4.2 | All     | -optical PPM-HP Router                                   | 78    |

|     | 4.2.1   | PPM                                                      | 78    |

|     | 4.2.2   | PPM-HP                                                   | 79    |

| 4.3 | Op      | tical Switch Control Module                              | 85    |

| 4.4 | Mu      | altiple-hop and Optical Signal-to-Noise Ratio            | 87    |

| 4.5 | Sin     | nulation Results and System Performance                  | 88    |

| 4.6 | Sur     | nmary                                                    | 100   |

| CHAPT        | ER 5ULTRA-FAST ALL-OPTICAL PACKET SWITCHED R | OUTER  |

|--------------|----------------------------------------------|--------|

| WITHN        | AULTIPLE PPRTS                               | 102    |

| 5.1          | Introduction                                 | 102    |

| 5.2          | Multiple-PPRTs                               | 103    |

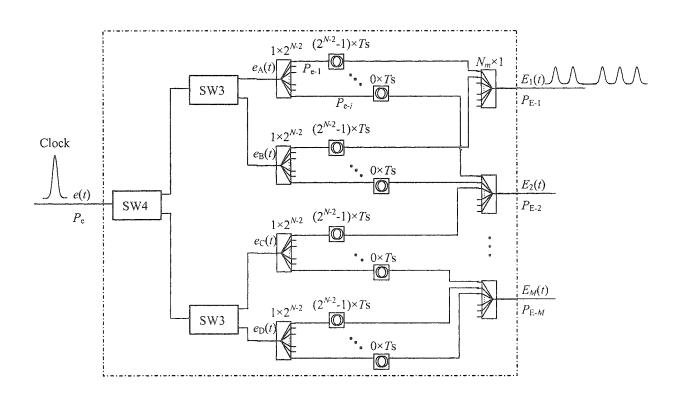

| 5.3          | Multiple-PPRT Generator                      | 106    |

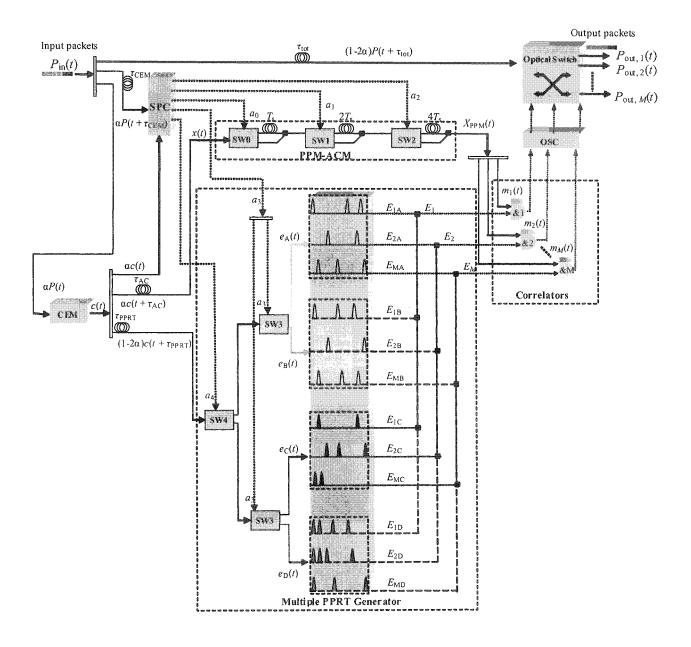

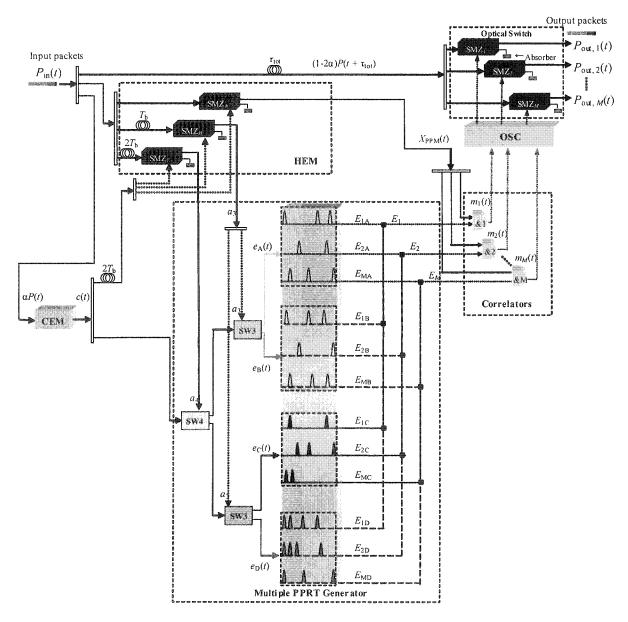

| 5.4          | Node Architecture                            | 108    |

| 5.5          | Simulation Results                           | 113    |

| 5.6          | Summary                                      | 121    |

| СНАРТ        | ER 6ALL-OPTICAL PACKET-SWITCHED ROUTER V     | VITH A |

| HYBRII       | D HEADER ADDRESS FORMAT                      | 123    |

| 6.1          | Introduction                                 | 123    |

| 6.2          | Hybrid Header Address                        | 124    |

| 6.3          | Node Architecture                            | 128    |

| 6.4          | Simulation Results                           | 130    |

| 6.5          | Summary                                      | 138    |

| СНАРТ        | ER 7 MULTIPLE WAVELENGTH ROUTER FOR WDM SYS  | STEM   |

| 000000000000 | •••••••••••••••••••••••••••••••••••••••      | 140    |

| 7.1          | Introduction                                 | 140    |

| 7.2          | Router Architecture                          | 141    |

| 7.3          | Simulation Results                           | 145    |

| 7.4          | Summary                                      | 156    |

| CHAPT        | ER 8 CONCLUSIONS AND FUTURE WORK             | 158    |

| 8.1          | Conclusions                                  | 158    |

| 8.2          | Future Work                                  | 162    |

| ADDENI       | DIY A VIRTUAL PHOTONIC SIMILATION SOFTWARE   | 164    |

| APPENDIX – B SYMMETRIC MACH-ZEHNDER        | 166  |

|--------------------------------------------|------|

| APPENDIX – C SOA GAIN RECOVERY TIME        | 169  |

| APPENDIX – D CLOCK EXTRACTION MODULE (CEM) | 170  |

| REFERENCES                                 | .173 |

## **GLOSSARY OF ACRONYMS**

2R Reshaping and Re-amplification

3R Reshaping, Re-amplification and Retiming

AM Amplitude Modulation

AOFF All-Optical Flip-Flop

AOLS All-Optical Label Switching

ASE Amplified Spontaneous Emission

ATM Asynchronous Transfer Mode

BER Bit Error Rate

CB Conduction Band

CCW Counter Clockwise

CEM Clock Extraction Module

CLK Clock

CP Control Pulse

CPMZ Colliding-Pulse Mach-Zehnder

CR Contrast Ratio

CRT Conventional Routing Table

CXT Crosstalk

CW Clockwise

DCF Dispersion Compensation Fibre

DFB Distributed-Feedback

DWDM Dense Wavelength Division Multiplexing

EDFA Erbium-Doped Fibre Amplifier

EDWA Erbium-Doped Waveguide Amplifier

FBG Fibre Bragg Grating

FDL Fibre Delay Line

FWHM Full Width at Half Maximum

FWM Four Wave Mixing

HEM Header Address Extraction

IP Internet Protocol

JET Just-Enough-Time

LAN Local Area Network

MAN Metropolitan Area Network

MEMS Micro-Electro-Mechanical Systems

MPPRT Multiple Pulse Position Routing Table

MQW Multi-Quantum-Well

MSB Most Significant Bit

MZI Mach-Zehnder Interferometer

NF Noise Figure

NOLM Nonlinear Optical Loop Mirror

OADM Optical Add/Drop Multiplexer

OBS Optical Burst Switching

OCS Optical Circuit Switching

O-E-O Optical-to-Electrical-to-Optical

OOK On-Off Keying

OPS Optical Packet Switching

OSI Open System Interconnection

OS All-Optical Switch

OSC OS Control

OSNR Optical Signal to Noise Ratio

OXC Optical Crossconnect

PBS Polarisation Beam Splitters

PC Polarisation Controller

PDH Plesiochronous Digital Hierarchy

PM Polarisation Maintaining

PoS Packet over SDH/SONET

PPM Pulse-Position-Modulation

PPM-HP Pulse-Position-Modulation Header Processing

PPRT Pulse Position Routing Table

PSI Polarisation Sensitive Optical Isolator

RAM Random Access Memory

RZ Return to Zero

SDH Synchronous Digital Hierarchy

SMF Single Mode Fibre

SMZ Symmetric Mach-Zehnder

SOA Semiconductor Optical Amplifier

SONET Synchronous Optical Network

SPC Serial to Parallel Converter

STM Synchronous Transport Module

STS Synchronous Transport Signal

SW Switching Window

TAG Tell-And-Go

TAW Tell-And-Wait

TOAD Terahertz Optical Asymmetric Demultiplexer

UNI Ultrafast Nonlinear Interferometer

VB Valence Band

WAN Wide Area Network

XGM Cross Gain Modulation

XPM Cross Phase Modulation

# **GLOSSARY OF SYMBOLS**

Optical loss of SOA α Linewidth enhancement factor of SOA  $\alpha_{\mathsf{LEF}}$ Current injection efficiency of SOA  $\eta_i$ Γ Confinement factor of SOA Spontaneous recombination lifetime of the carriers  $\tau_{\mathrm{s}}$ Total required time for PPM address correlation  $\tau_{\rm tot}$ The phase difference Δφ Optical bandwidth of the system (i.e. filter optical bandwidth)  $B_{\rm o}$ Extracted clock signal c(t)Thickness of the active region of SOA d The electronic charge e E(t)PPRT entry  $G_{OS}$ Gain of optical switch GGain of SOA Differential gain of SOA g Material gain of SOA gm Gain coefficient of SOA  $g_0$ I Injection current of SOA Length of the active region of SOA L

$L_{\text{combiner}}$  Insertion loss of the combiner

$L_{\text{MPPRT}}$  Total power loss due to multiple PPRT generator

$L_{\rm splitter}$  Insertion loss of the splitter

m(t) Match signal

$n_{\rm sp}$  The spontaneous-emission factor

N Carrier density of SOA

$N_0$  Carrier density (at transparency) of SOA

$P_{\text{ase}}$  ASE noise power

$P_{in}(t)$  Input power

$P_{\rm nt}$  Sum of the output signal power of all non-target channels

$P_{\text{OSC-in}}$  Minimum required power of the input pulse for OSC

$P_{\text{OSC-out}}$  Peak power of the CP stream generated by OSC

$P_{out}(t)$  Output power

$P_{\rm t}$  Sum of the output signal power of the target channel

r<sub>AM</sub> Amplitude modulation ratio

$r_{\text{on/off}}$  On/off contrast ratio

R<sub>b</sub> Data bit rate

$R_{\text{MPPRT}}$  Correlation-time gain by employing multiple PPRTs

$R_{PPRT}$  Correlation-time gain by employing PPRT

$T_{\text{AND}}$  Time interval required for two successive AND operations

T<sub>b</sub> Bit duration

$T_{\rm CRT}$ Address correlation time of conventional routing table Address correlation time of multiple PPRTs  $T_{\mathrm{MPPRT}}$ Address correlation time of PPRT  $T_{\mathtt{PPRT}}$  $T_{\rm s}$ PPM time slot Switching window width  $T_{\rm sw}$ Group velocity of the control pulses  $V_{\mathsf{g}}$ Width of the SW profile W(t)Width of the active region of SOA w

PPM header frame

$X_{PPM}(t)$

# LIST OF FIGURES

| Figure | 1.1 BL products against the different communication technologies2                                     |

|--------|-------------------------------------------------------------------------------------------------------|

| Figure | 1.2 An optical core network with 16 edge nodes                                                        |

| Figure | 2.1 Fibre loss (dB/km) versus wavelength (μm)                                                         |

| Figure | 2.2 A typical optical network showing LAN, MAN, and WAN                                               |

| Figure | <b>2.3</b> The OSI model                                                                              |

| Figure | <b>2.4</b> The telecommunication core networks architecture [60]                                      |

| Figure | 2.5 A typical format of an optical packet                                                             |

| Figure | 2.6 A block diagram of an optical packet-switched router architecture25                               |

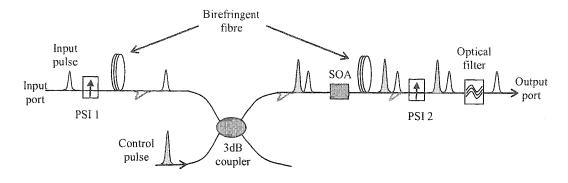

| Figure | <b>2.7</b> The structure of UNI [106, 178]                                                            |

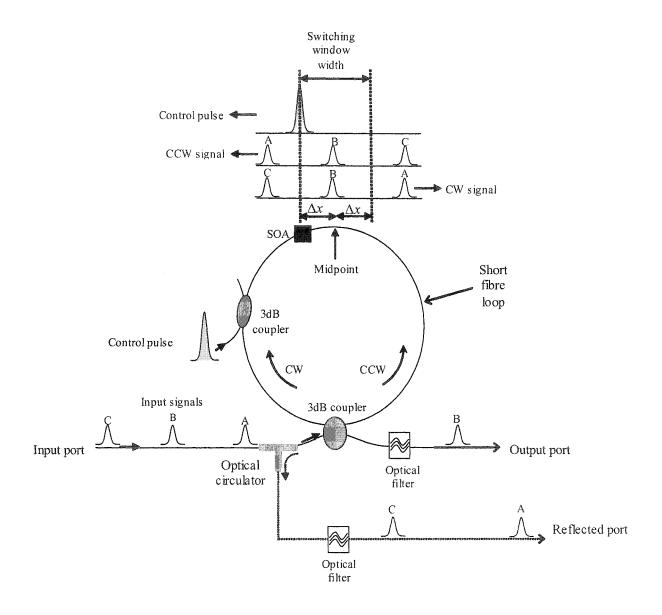

| Figure | <b>2.8</b> The structure of TOAD [178]                                                                |

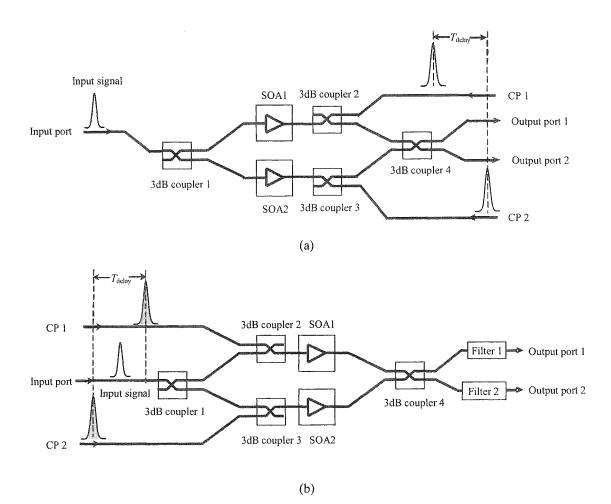

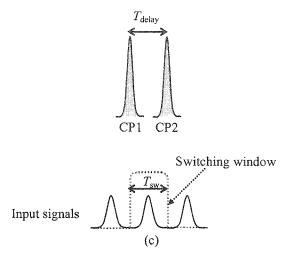

| _      | 2.9 Two basic structures of MZI switch: (a) CPMZ (b) SMZ, and (c) MZI switching window [178]          |

| Figure | 3.1 (a) Diagram of a SOA and (b) p-n junction in SOA                                                  |

| Figure | <b>3.2</b> Three radiative phenomena in the SOA [200]38                                               |

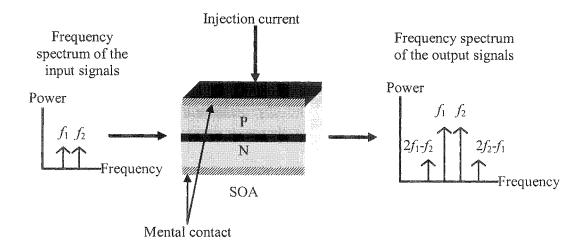

| -      | 3.3 SOA nonlinearities (the output responses are simplified for clarity): (a) XGM & XPM and (b) FWM40 |

| Figure | <b>3.4</b> SMZ structure                                                                              |

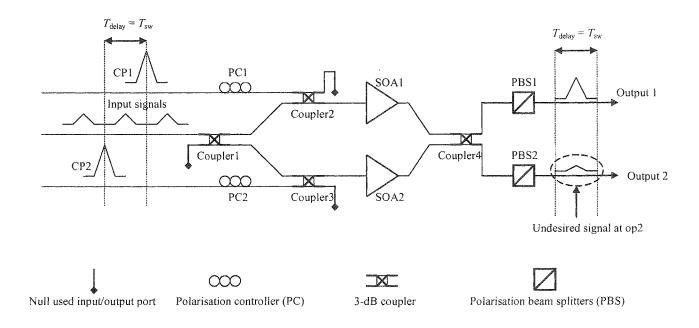

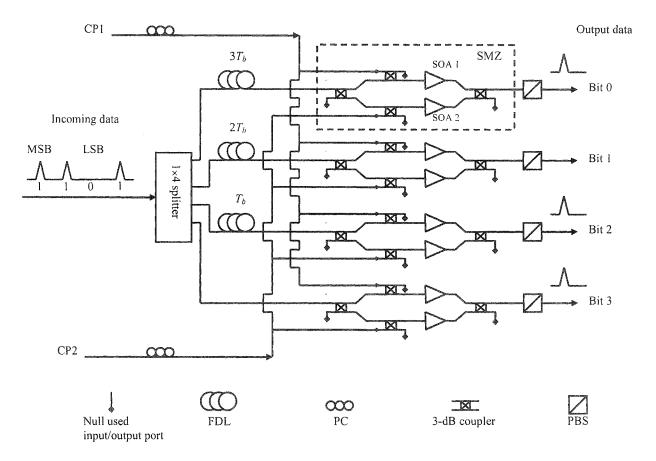

| Figure | 3.5 SPC system block diagram                                                                          |

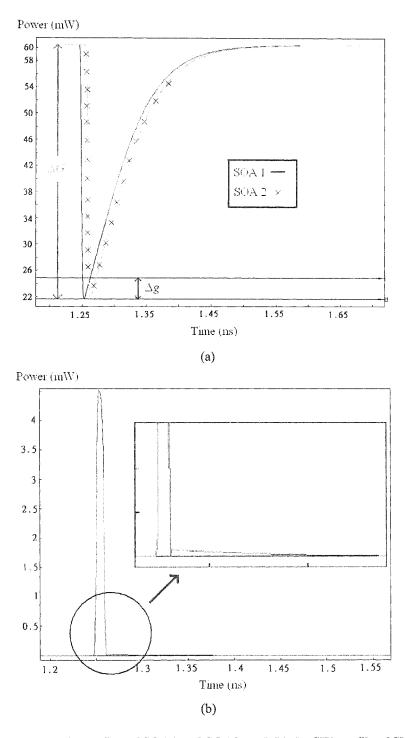

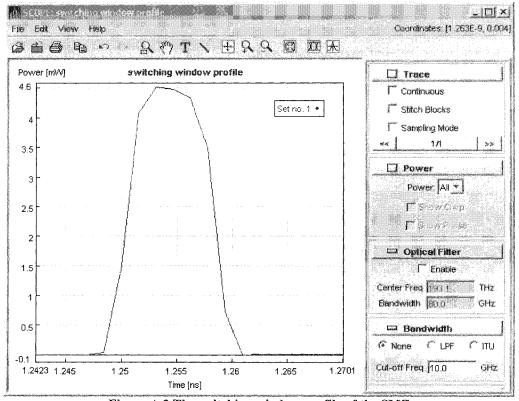

|        | 3.6 (a) The gain profiles of SOA1 and SOA2, and (b) the SW profile of SMZ output1                     |

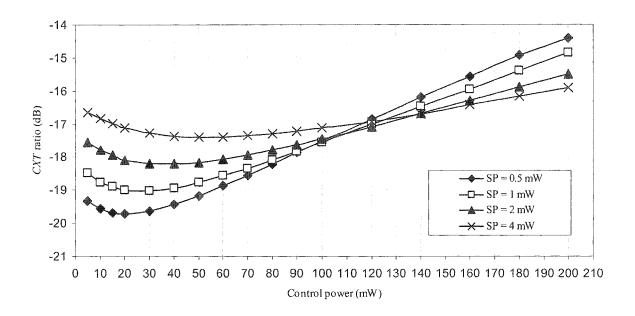

| Figure | 3.7 Crosstalk versus (a) control power, and (b) FWHM of CP and SP50                                   |

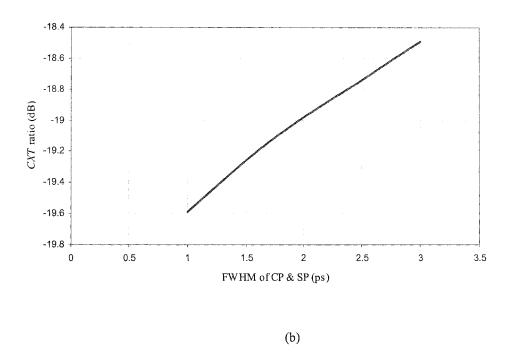

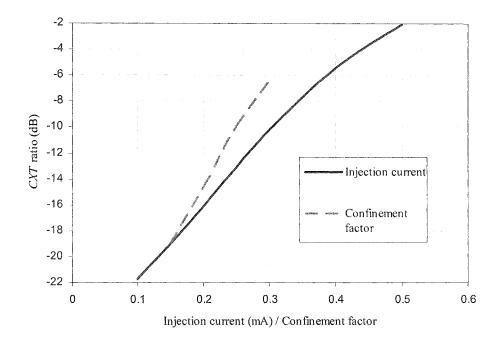

| _      | 3.8 Crosstalk versus (a) CP1 and CP2 delay times, and (b) linewidth confinement factor                |

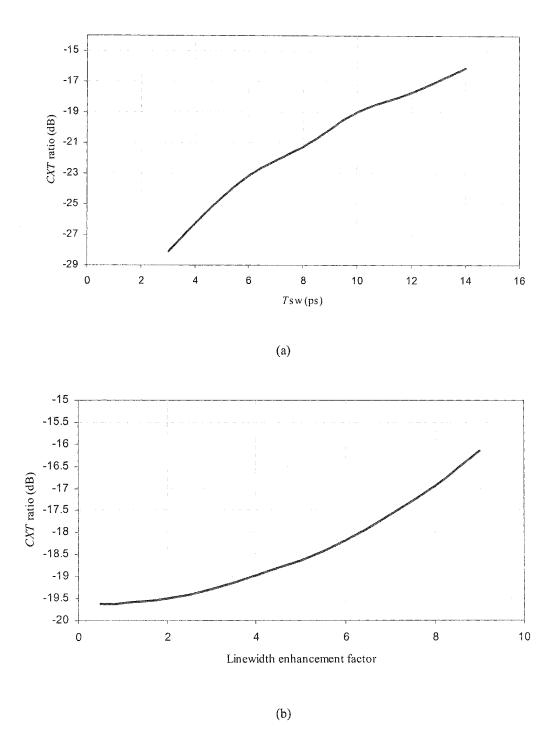

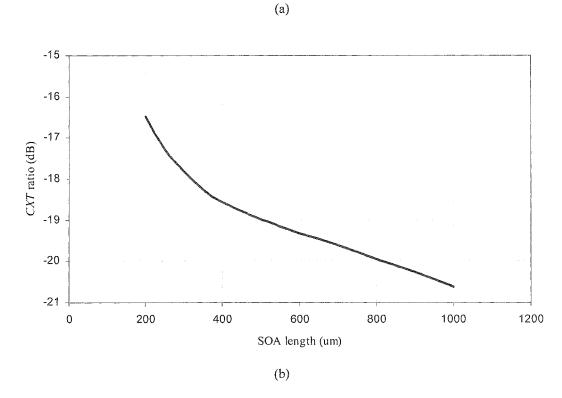

|        | 3.9 Crosstalk versus (a) inject current and confinement factor, and (b) SOA length                    |

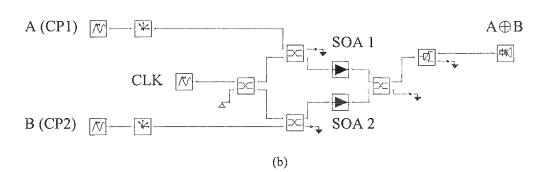

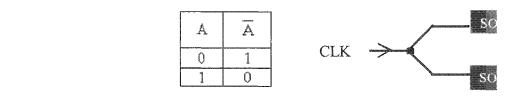

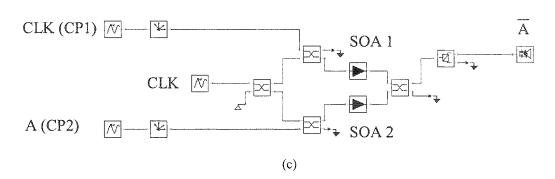

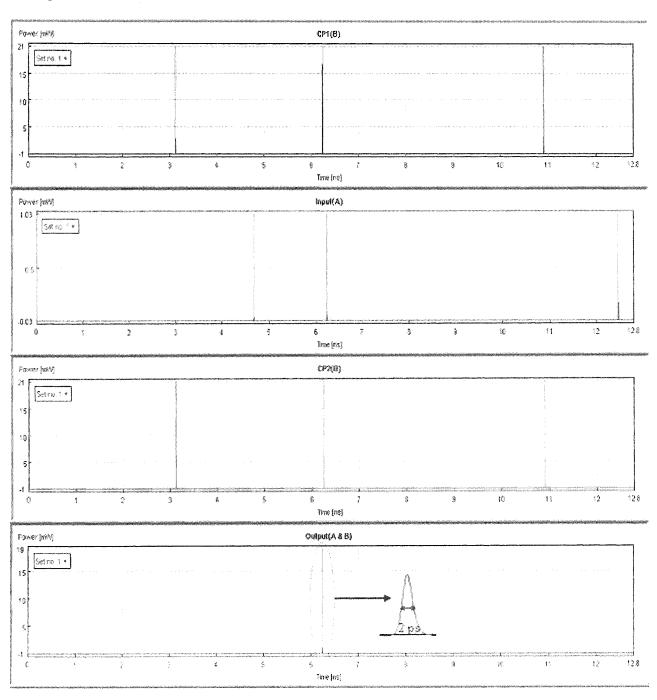

| Figure 3.10 (a) AND, (b) XOR and (c) NOT gates based on SMZ56                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

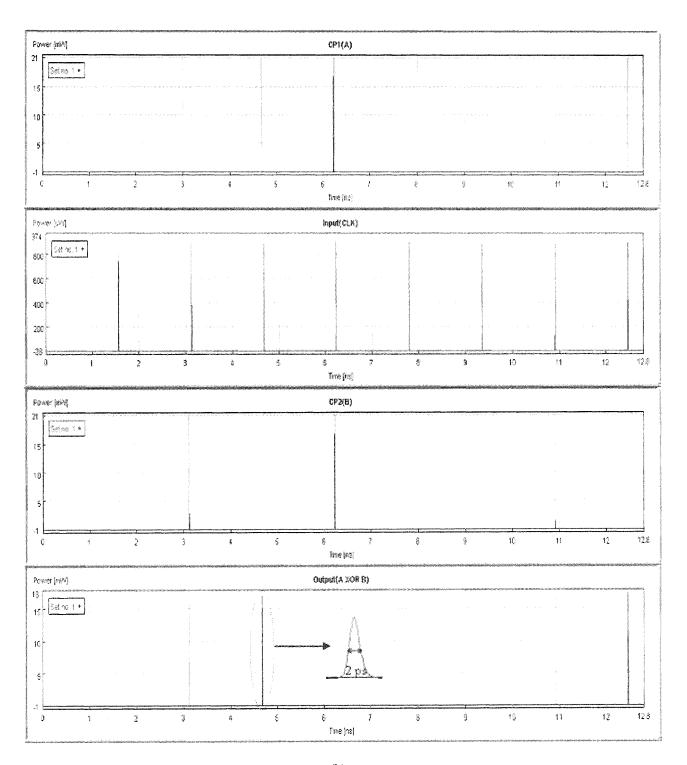

| Figure 3.11 Simulation results of all-optical (a) AND, (b) XOR and (c) NOT gates based on the SMZ (also see the enlarged pulse waveforms)                                                                              |

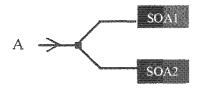

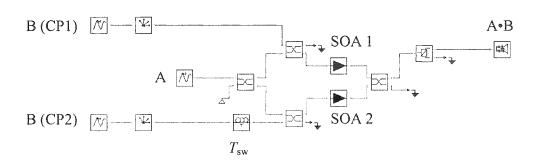

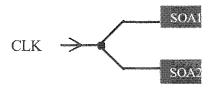

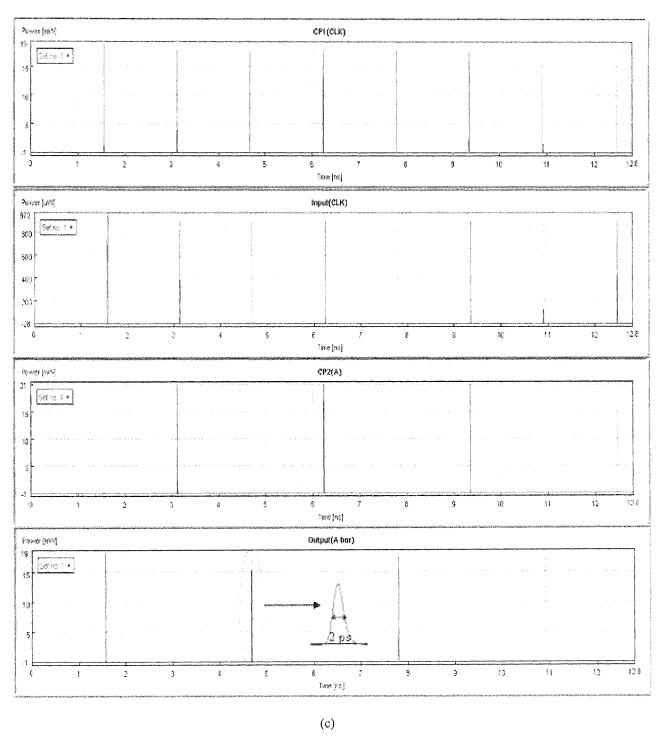

| Figure 3.12 (a) An all-optical 1×2 switch, and (b) VPI based model                                                                                                                                                     |

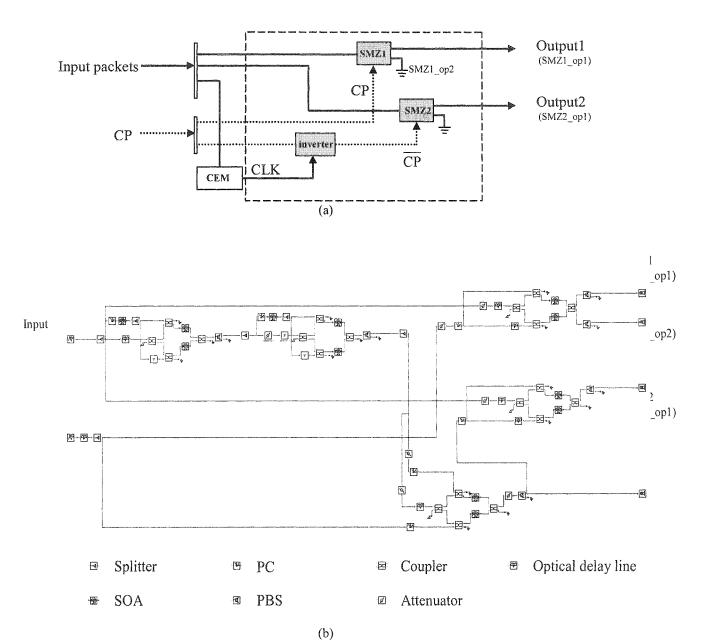

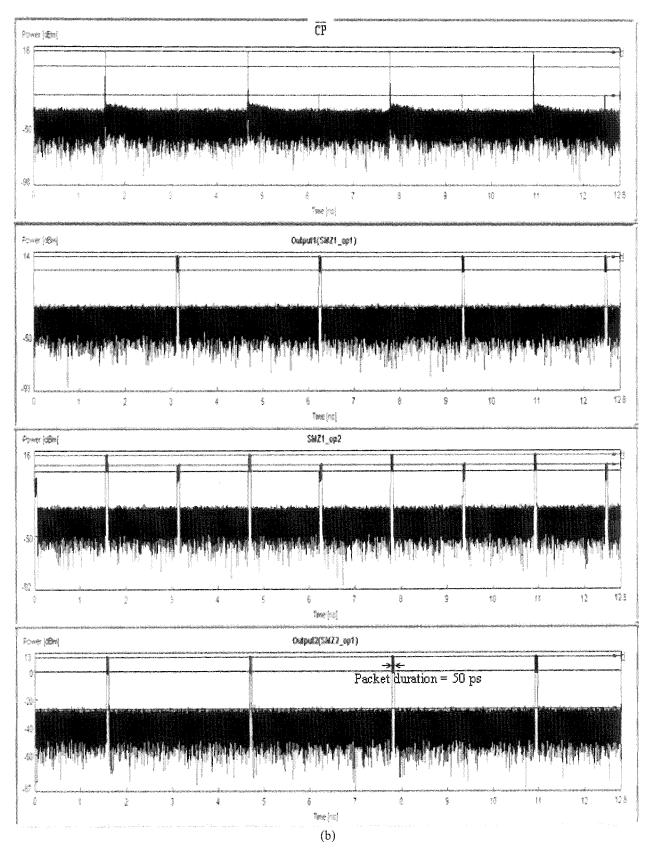

| <b>Figure 3.13</b> (a) Output waveforms (also see the enlarged pulse waveforms), and (b) $CR$ ratio observed at $\overline{CP}$ , the proposed 1×2 switch output 1, output 2, and SMZ1_op2                             |

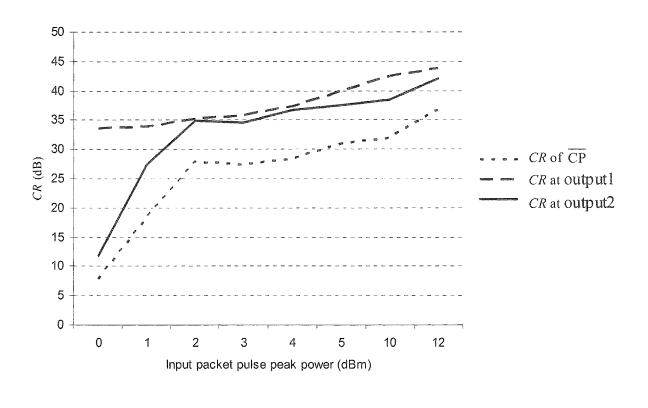

| Figure 3.14 The observed contrast ratio (CR) against (a) the input packet power and (b) the control pulse power                                                                                                        |

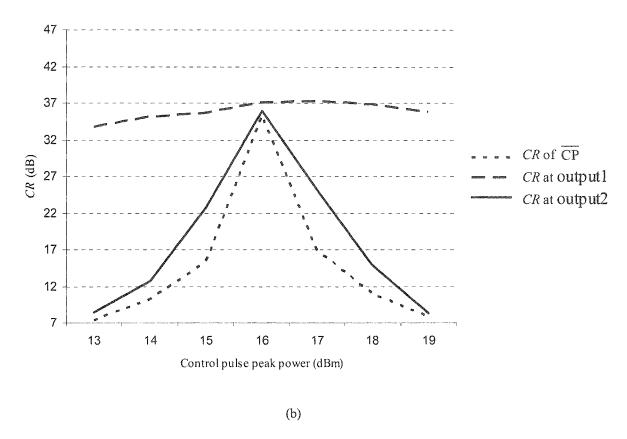

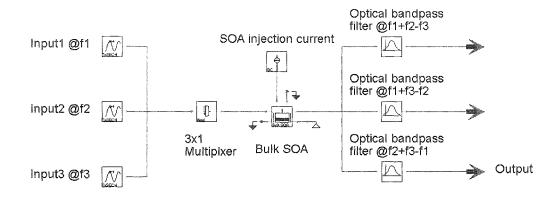

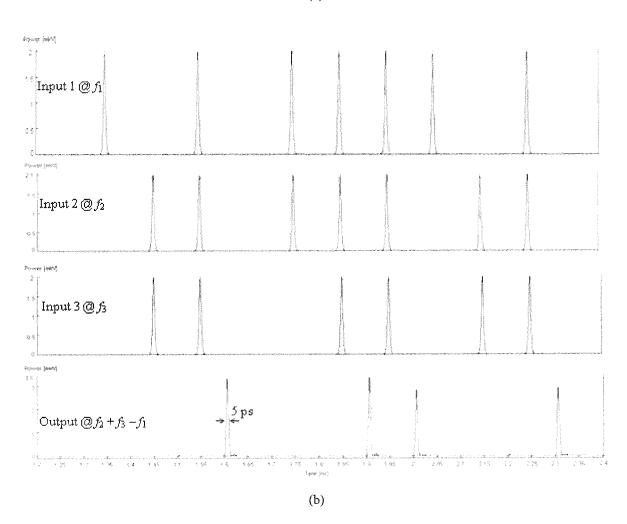

| Figure 3.15 Schematic of a <i>M</i> -input AND gate based on SOA-FWM69                                                                                                                                                 |

| Figure 3.16 (a) VPI schematic for a 3-input AND gate based on FWM in SOA(b)  Three inputs X <sub>1</sub> , X <sub>2</sub> , X <sub>3</sub> and output Y, respectively, of AND gate operating at the bitrate of 10 Gb/s |

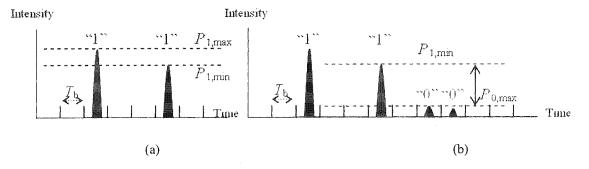

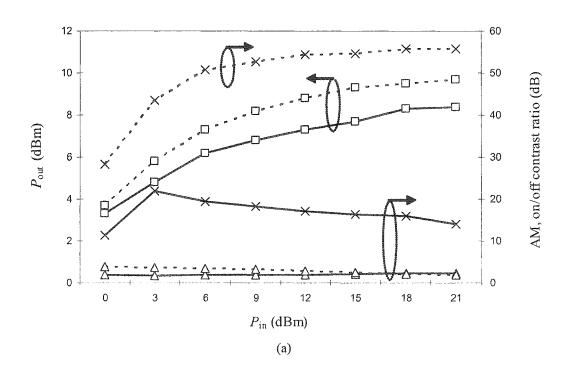

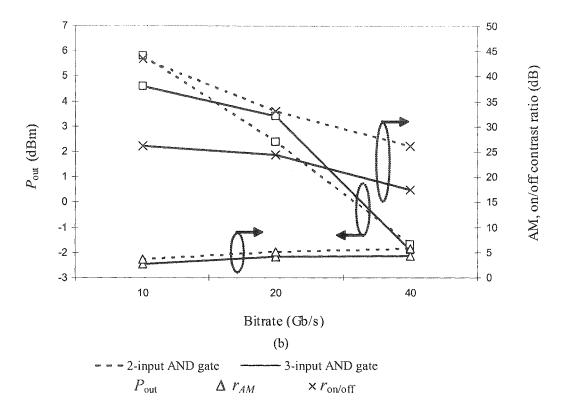

| Figure 3.17 (a) AM ratio and (b) on/off contrast ratio                                                                                                                                                                 |

| Figure 3.18 Output power, AM and on/off contrast ratio against (a) input power and (b) bit rate                                                                                                                        |

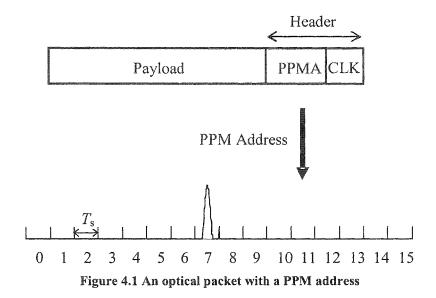

| Figure 4.1 An optical packet with a PPM address                                                                                                                                                                        |

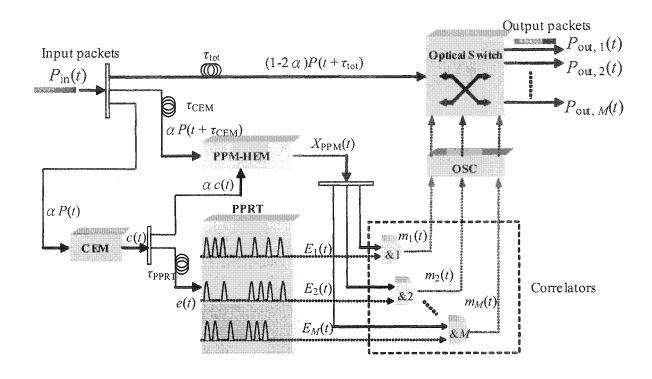

| <b>Figure 4.2</b> A schematic block diagram of a 1× <i>M</i> PPM header processing (PPM-HP) based router                                                                                                               |

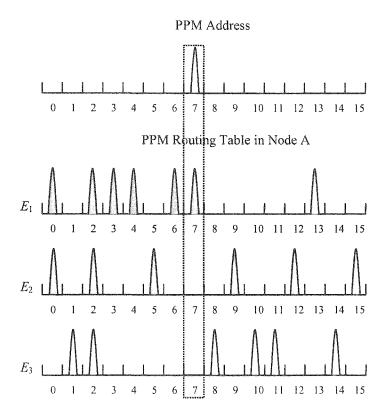

| Figure 4.3 Correlation between PPM address and PPRT entries                                                                                                                                                            |

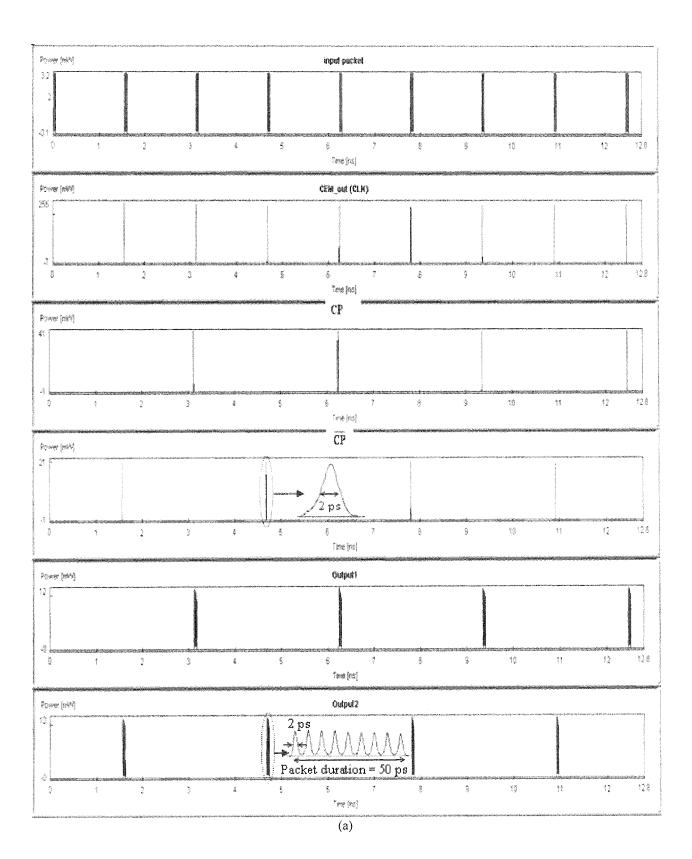

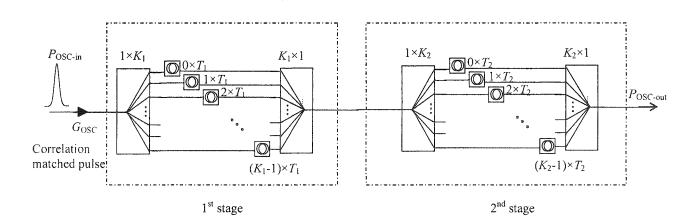

| Figure 4.4 (a) The 2-stage structure of the multiple-pulse generator (i.e. OSC), and (b) the process of multiple-pulse stream                                                                                          |

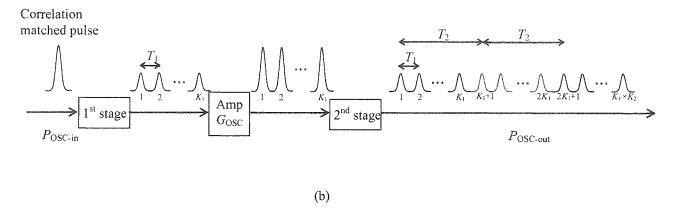

| <b>Figure 4.5</b> Signal and ASE noise power propagation from the source edge node to the target edge node via <i>H</i> core nodes                                                                                     |

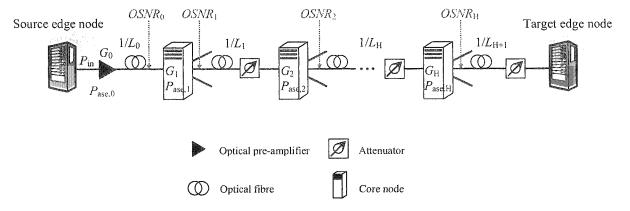

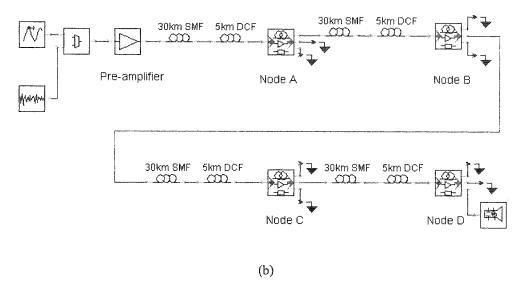

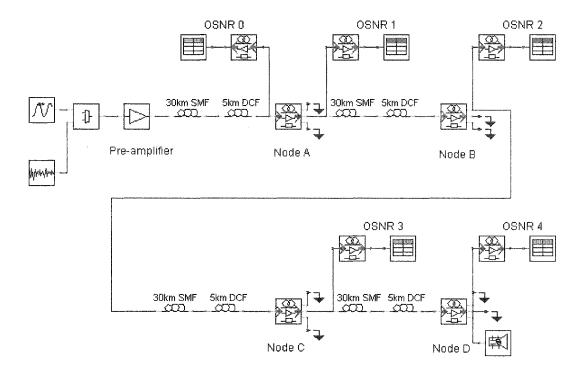

| <b>Figure 4.6</b> The VPI simulation schematic block diagram for (a) a router (node) architecture four-hop routing, and (b) four-hop routing90                                                                         |

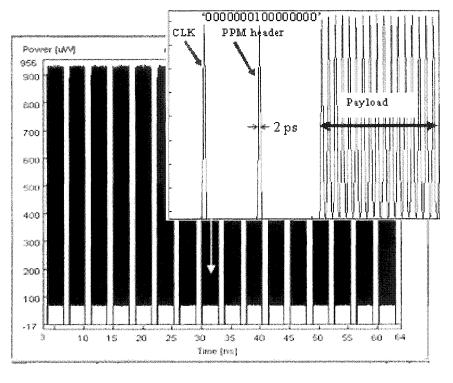

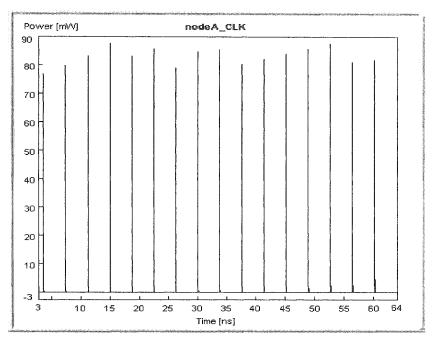

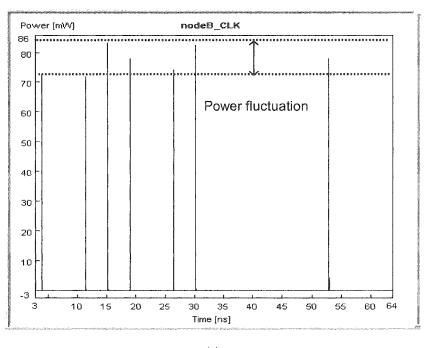

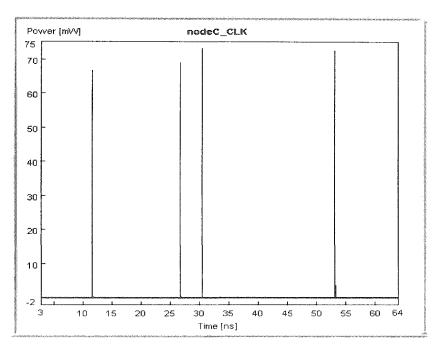

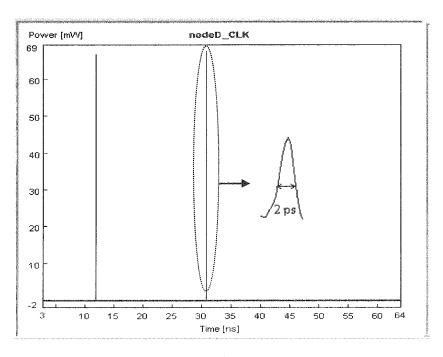

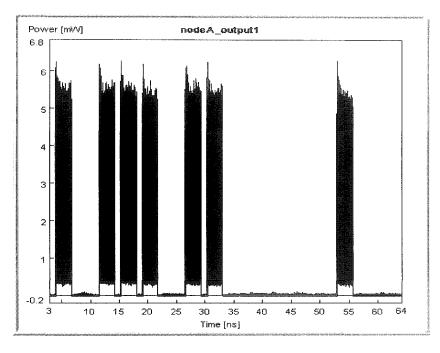

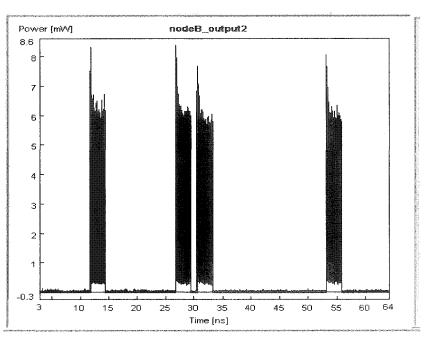

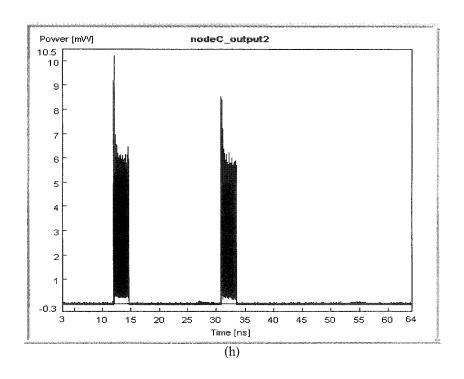

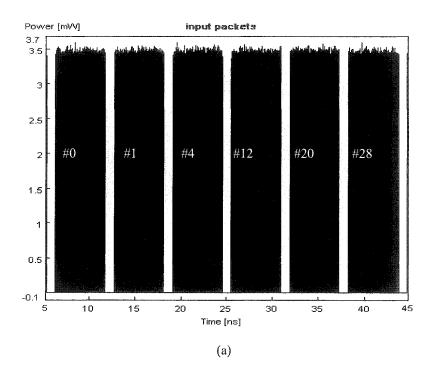

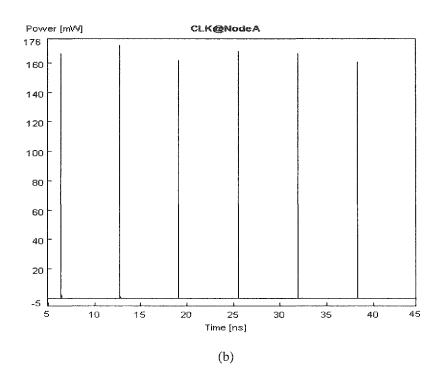

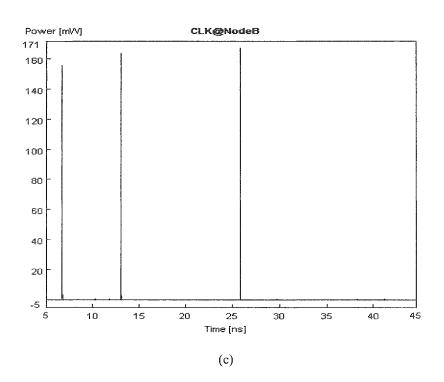

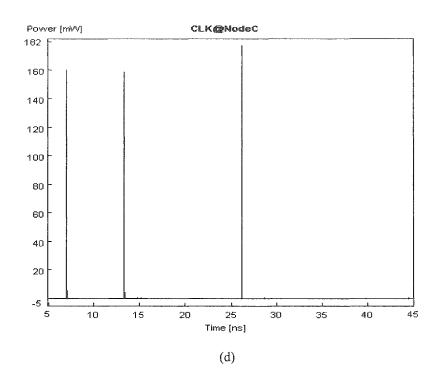

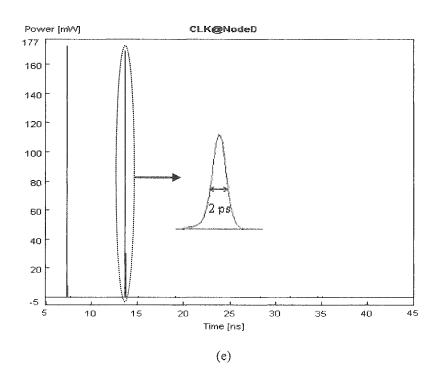

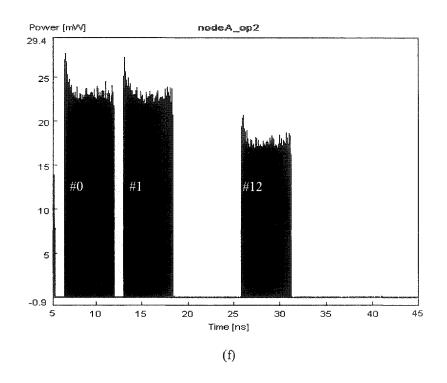

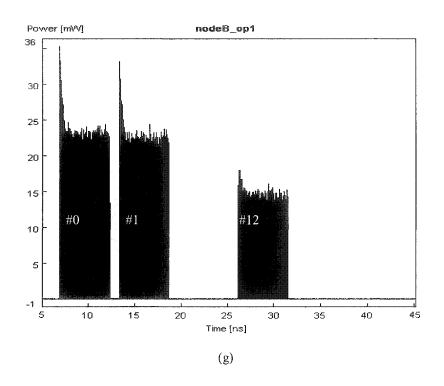

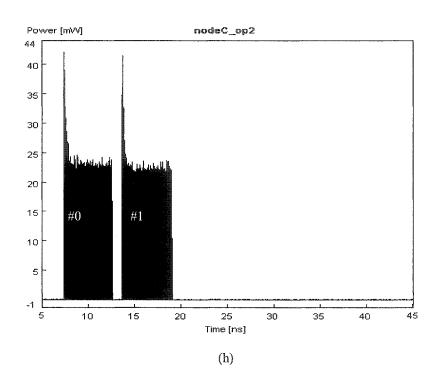

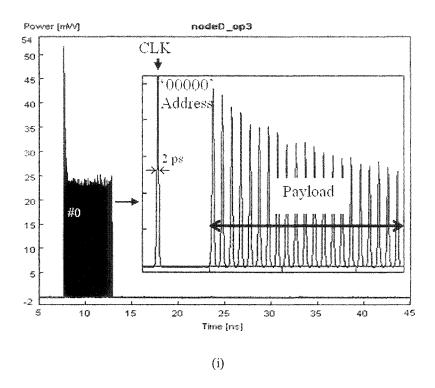

| Figure 4.7 Time waveforms; (a) input packet packets at node A, (b) extracted clock at node A, (c) extracted clock at node B, (d) extracted clock at node C, (e)                                                        |

|        | extracted clock at node D, (f) switched packets at node A – output1, (g) switched packets at node B – output2, (h) switched packets at node C – output2, and (i) switched packets at node D – output3 (also see the enlarged                                                                                                                                                                                                                                                                                                                           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | waveforms)95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

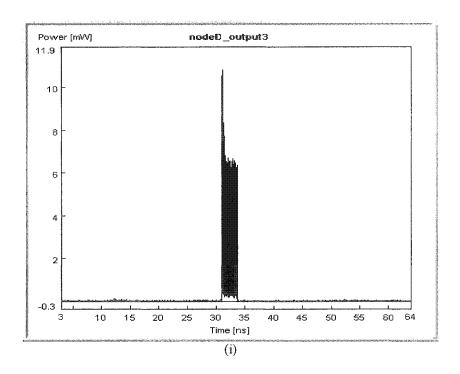

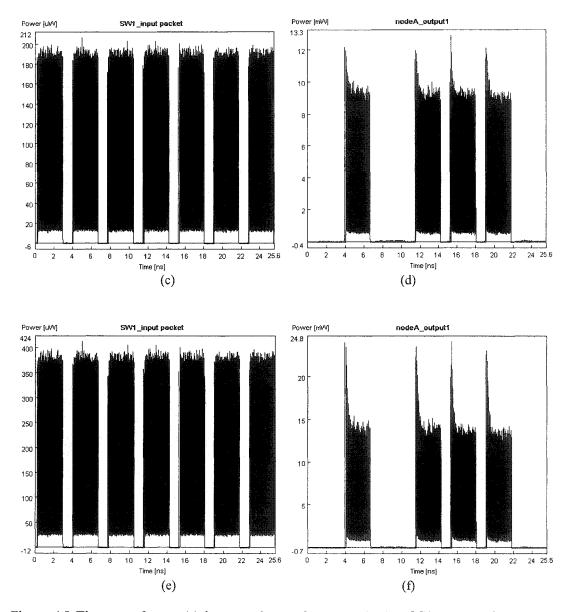

|        | 4.8 Time waveforms; (a) input packet packets at node A - OS1 (average input packet power = $100 \mu W$ ), (b) switched packets at node A - output1 (average input packet power = $100 \mu W$ ), (c) input packet packets at node A - OS1 (average input packet power = $200 \mu W$ ), (d) switched packets at node A - output1 (average input packet power = $200 \mu W$ ), (e) input packet packets at node A - OS1 (average input packet power = $400 \mu W$ ), (f) switched packets at node A - output1 (average input packet power = $400 \mu W$ ) |

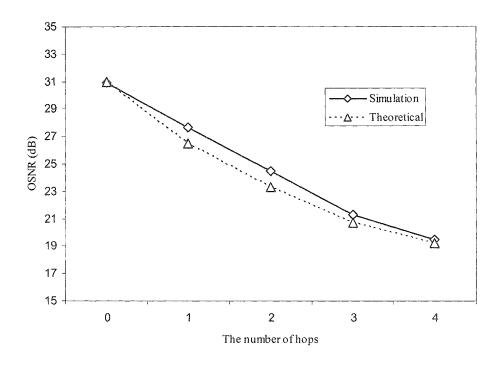

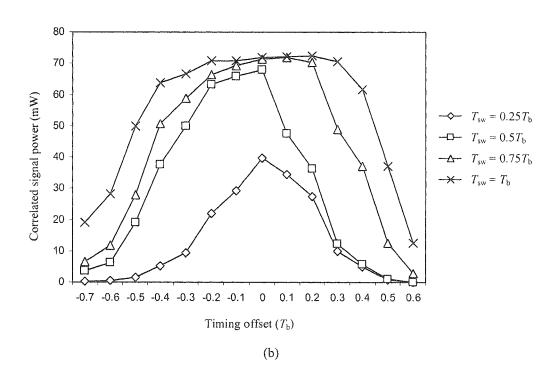

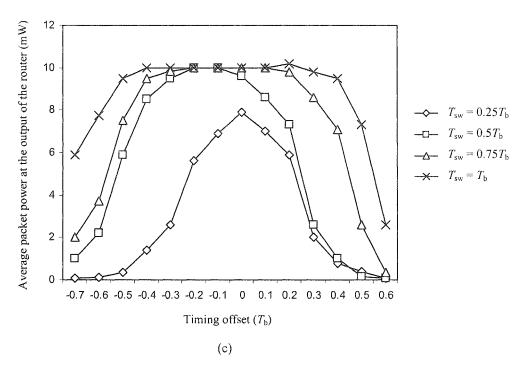

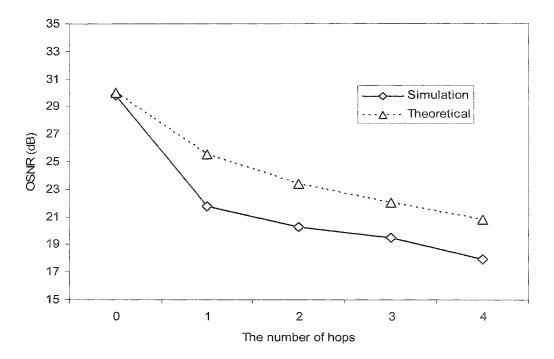

|        | <b>4.9</b> (a) OSNR against the number of hops, (b) power of correlated signal $m_k(t)$ , and (c) the average packet power at the output of the router99                                                                                                                                                                                                                                                                                                                                                                                               |

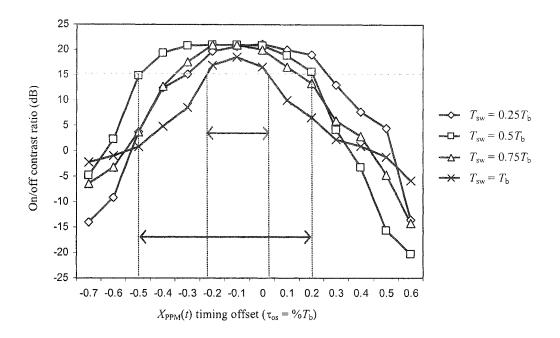

| Figure | <b>4.10</b> The on/off contrast ratio against the timing offset of PPM address 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

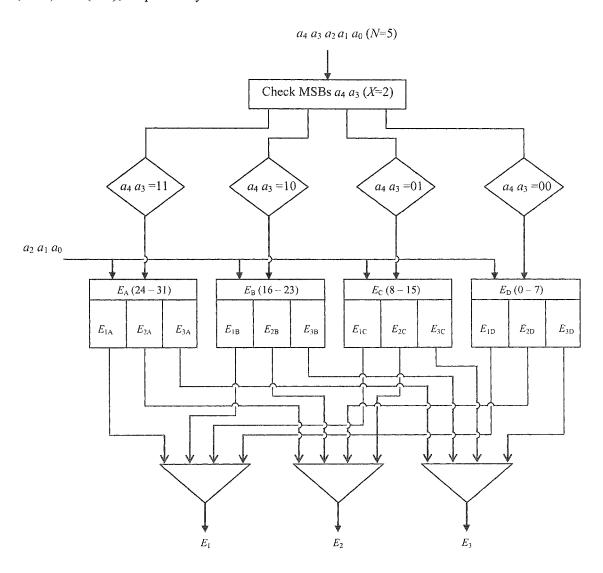

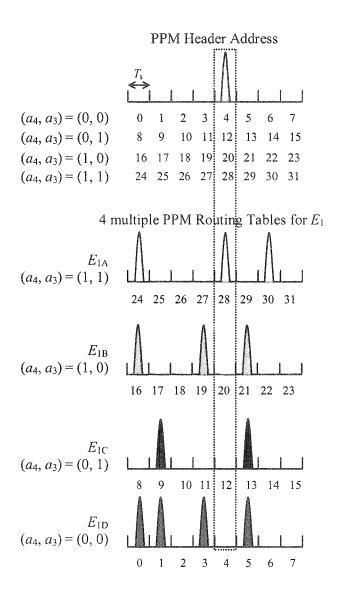

|        | <b>5.1</b> A block diagram of multiple PPRT ( $E_{1A}$ , $E_{2A}$ , $E_{3A}$ ,, $E_{3D}$ ) for 5-bit packet header address                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure | <b>5.2</b> Multiple PPRT generator (for <i>X</i> =2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _      | <b>5.3</b> A schematic block diagram of node structure with multiple PPRTs for 5-bit packet header address $(N = 5, X = 2)$                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure | <b>5.4</b> Correlation between PPM address with one of 4 multiple PPRT entries 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure | <b>5.5</b> The VPI simulation setup for four-hop routing115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

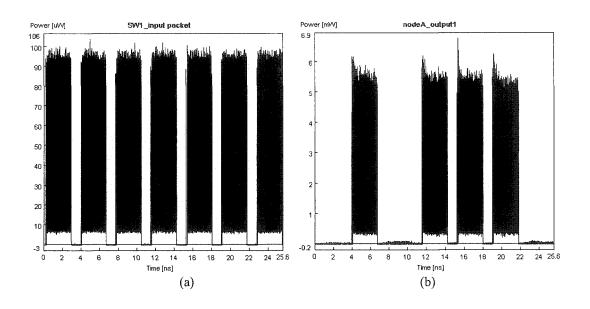

| Ü      | <b>5.6</b> Time waveforms; (a) input packet at node A, (b)-(e) extracted clock at nodes A, B, C, and D, and (f)-(i) switched packets at nodes A – output2, B – output1, C – output2, and D – output3 (also see the enlarged waveforms)120                                                                                                                                                                                                                                                                                                              |

| Figure | <b>5.7</b> Predicted and simulated OSNR performance against the number of hops                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

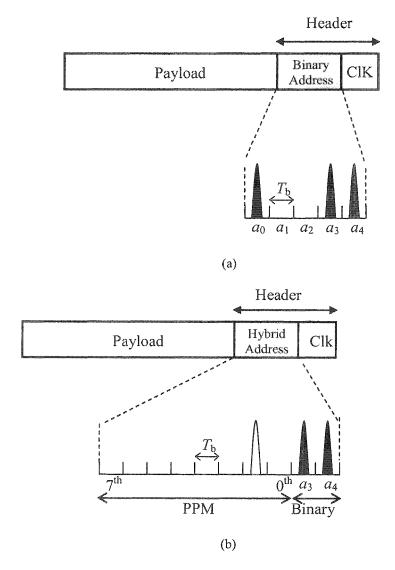

|        | <b>6.1</b> (a) An optical packet with N-bit conventional binary address pattern ( $N = 5$ ), (b) an optical packet with a hybrid header address format equivalent to N-bit conventional address pattern ( $N = 5$ ), $T_b$ is the bit duration                                                                                                                                                                                                                                                                                                         |

| ~      | <b>6.2</b> A schematic block diagram of node architecture for packets with hybrid header address (where <i>N</i> =5, <i>X</i> =2)                                                                                                                                                                                                                                                                                                                                                                                                                      |

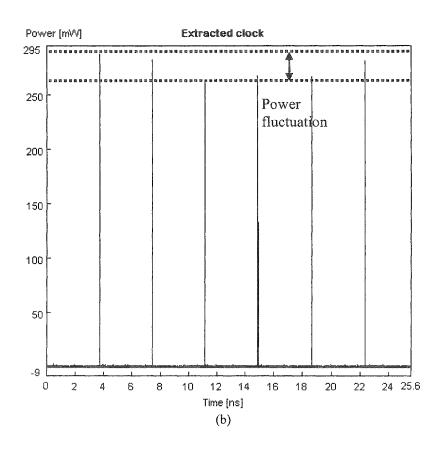

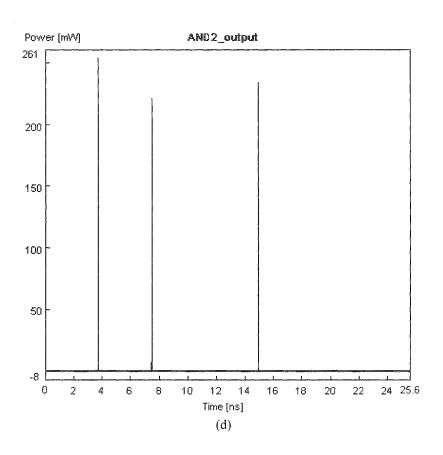

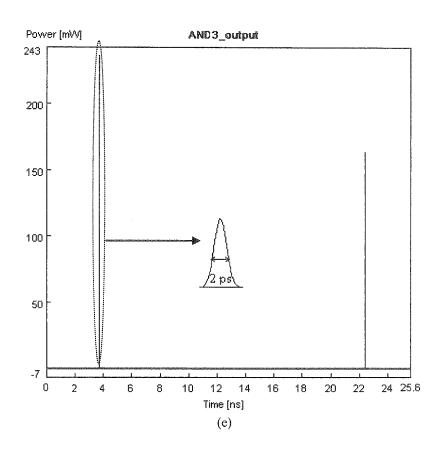

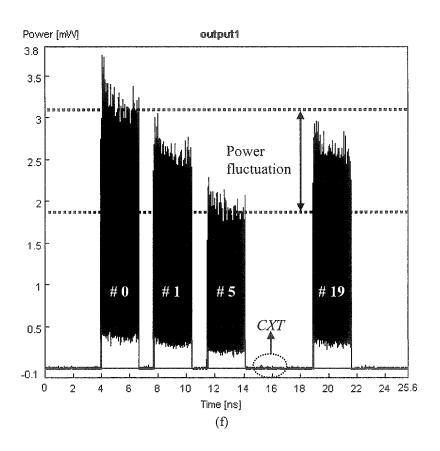

|        | <b>6.3</b> Time waveforms of (a) input packets, (b) extracted clock signals, (c) matched signals at AND gate 1, (d) matched signals at AND gate 2, (e)                                                                                                                                                                                                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | matched signals at AND gate 3, (f) switched packets at router's output 1, (g)                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | switched packets at router's output 2, and (h) switched packets at router's                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | output 3 (also see the enlarged waveforms)                                                                                                                                                                                                                                                                                                                                                                                                                                               |

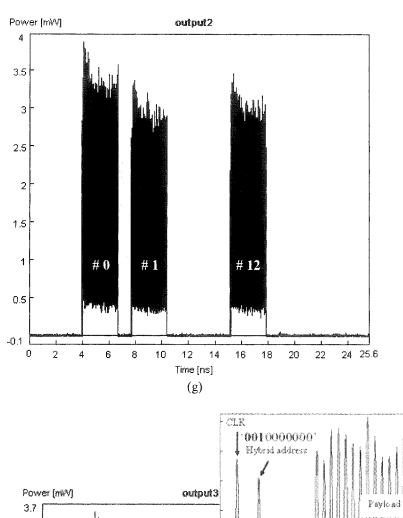

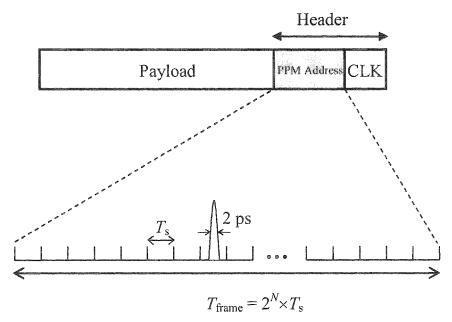

|        | 6.4 Packet guard time against the output intra-channel CXT (left x-axis), output packet power fluctuation (right x-axis) and the extracted clock power fluctuation (right x-axis)                                                                                                                                                                                                                                                                                                        |

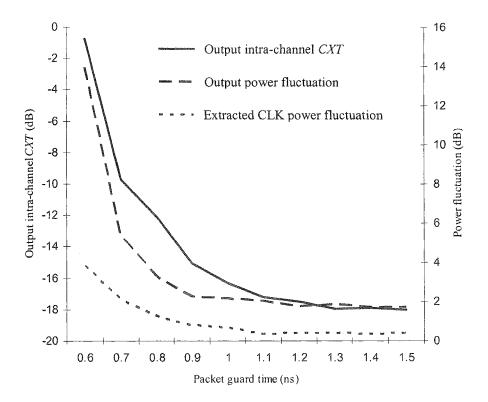

| Figure | 7.1 An optical packet with the PPM header address                                                                                                                                                                                                                                                                                                                                                                                                                                        |

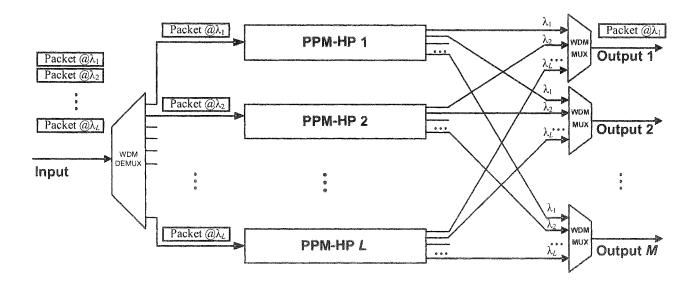

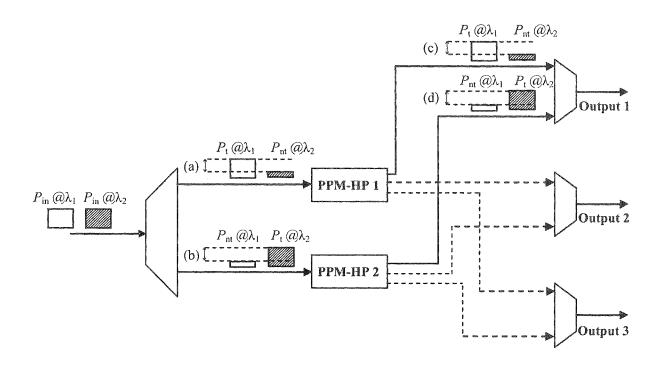

| Figure | <b>7.2</b> The WDM router architecture for $L = 2$ and $M = 3$                                                                                                                                                                                                                                                                                                                                                                                                                           |

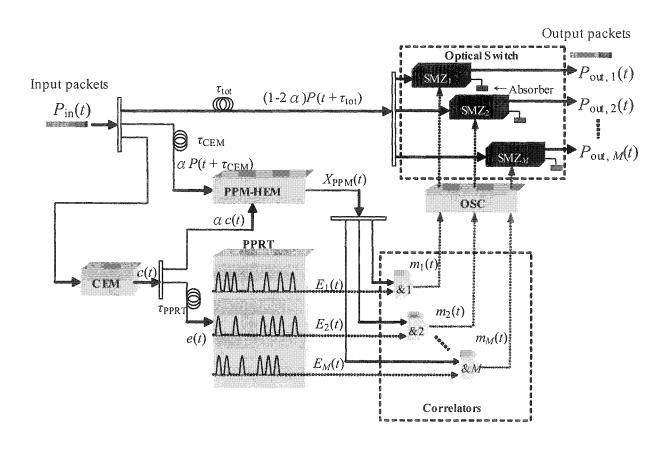

| Figure | <b>7.3</b> The schematic diagram of PPM-HP144                                                                                                                                                                                                                                                                                                                                                                                                                                            |

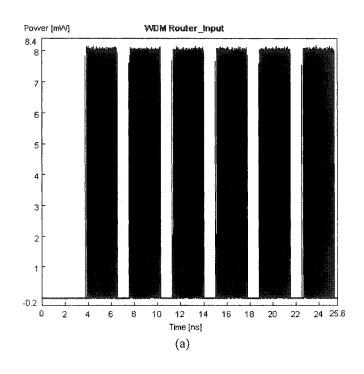

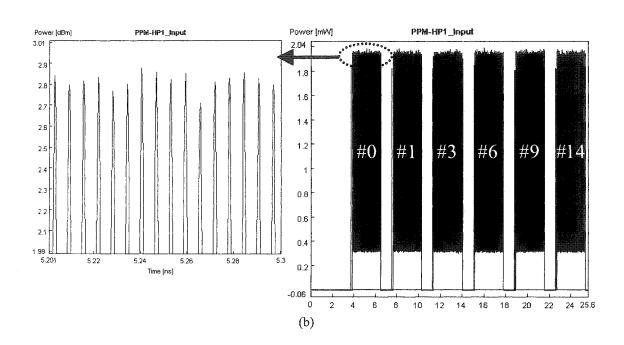

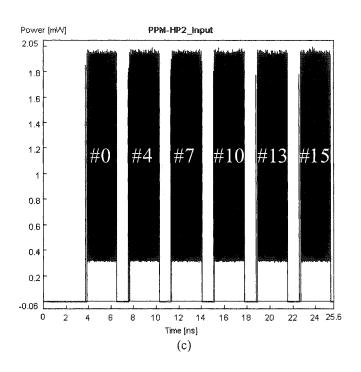

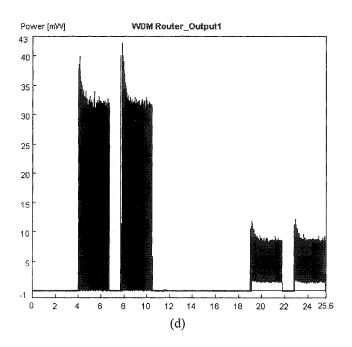

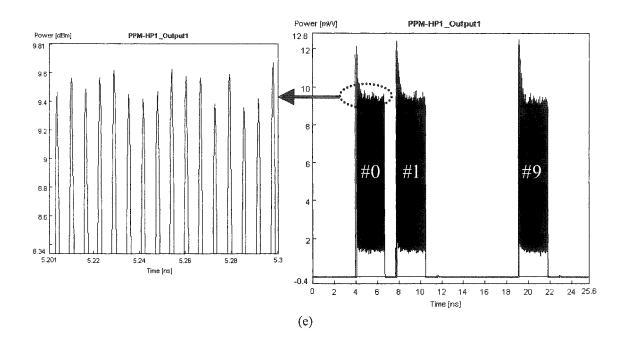

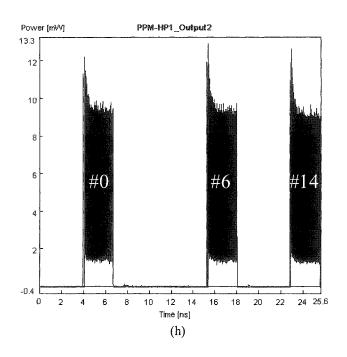

| -      | 7.4 Packets observed at (a) the input of the WDM router, (b) the input of the PPM-HP1 (the inset shows the power fluctuation observed at the input of PPM-HP1), (c) the input of the PPM-HP2, (d) the output 1 of the WDM router, (e) the output 1 of the PPM-HP1 (the inset shows the power fluctuation observed at the output 1 of PPM-HP1), (f) the output 1 of the PPM-HP2, (g) the output 2 of the WDM router, (h) the output 2 of the PPM-HP1, and (i) the output 2 of the PPM-HP2 |

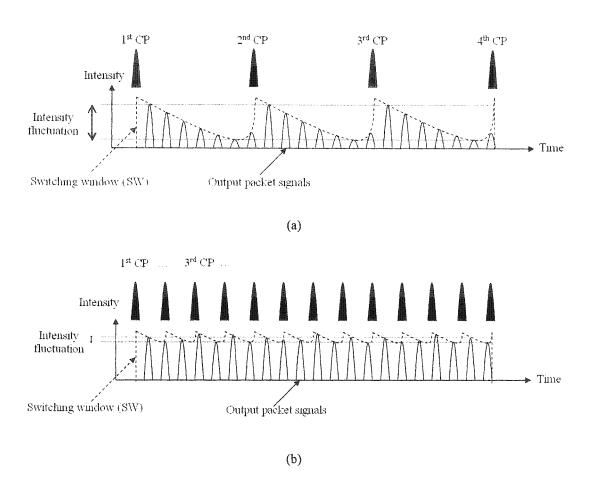

| 0      | 7.5 The output packet intensity fluctuation (a) is large as applying less CPs, and (b) the intensity fluctuation is reduced as applying more CPs152                                                                                                                                                                                                                                                                                                                                      |

| _      | 7.6 (a) The inter-channel CXT observed at input of PPM-HP1, (b) CXT observed at input of PPM-HP2, CXT observed at output1 of PPM-HP1, and (d) CXT observed at output1 of PPM-HP2                                                                                                                                                                                                                                                                                                         |

| C      | 7.7 The inter-channel crosstalk ( <i>CXT</i> ) observed at input of PPM-HP1&2 and output1 of PPM-HP1 & 2 against the channel spacing (the bandwidth of the WDM multiplexers and demultiplexer is 500 GHz)                                                                                                                                                                                                                                                                                |

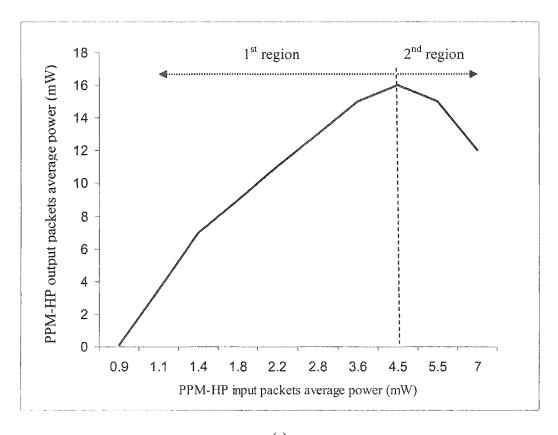

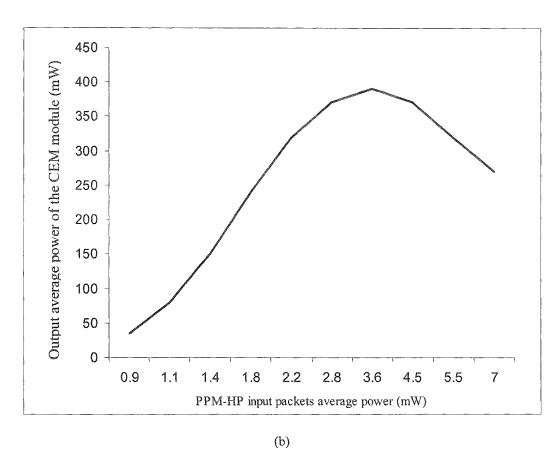

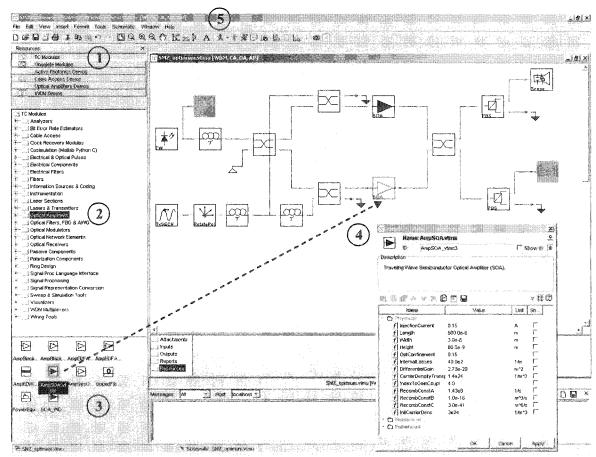

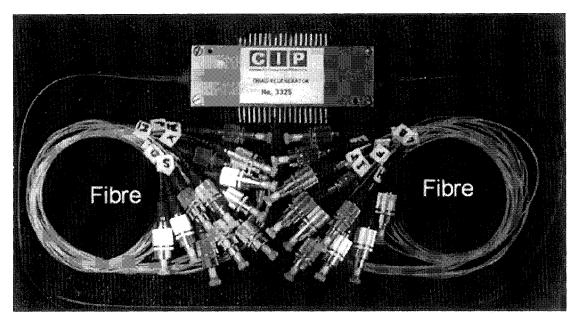

| 0      | 7.8 PPM-HP input packets average power versus (a) PPM-HP output packets average power, and (b) output average power of the CEM module                                                                                                                                                                                                                                                                                                                                                    |

# LIST OF TABLES

| Table 3.1 SOA simulation parameters    48                                                                            |

|----------------------------------------------------------------------------------------------------------------------|

| Table 3.2 Signal and control pulses default parameters    48                                                         |

| Table 3.3 SOA simulation parameters   54                                                                             |

| Table 3.4 Signal and control pulses default parameters    54                                                         |

| Table 3.5 SOA simulation parameters    62                                                                            |

| Table 3.6 Signal and control pulses default parameters    62                                                         |

| Table 3.7 Main simulation parameters    70                                                                           |

| Table 3.8 The bulk SOA parameters   70                                                                               |

| Table 4.1 (a) Conventional routing table with $2^N$ -entries and (b) its corresponding         PPRT with $M$ entries |

| Table 4.2 Simulation parameters   89                                                                                 |

| Table 5.1 The conversion of conventional RT to single PPRT and multiple PPRTs104                                     |

| Table 5.2 Simulation parameters   114                                                                                |

| Table 6.1 The conversion of conventional RT to single PPRT                                                           |

| Table 6.2 The conversion of conventional RT to multiple PPRTs    127                                                 |

| Table 6.3 Simulation parameters   131                                                                                |

| Table 7.1 The conventional and PPM based routing tables    142                                                       |

| Table 7.2 Simulation parameters   145                                                                                |

## **CHAPTER 1 INTRODUCTION**

#### 1.1 Background

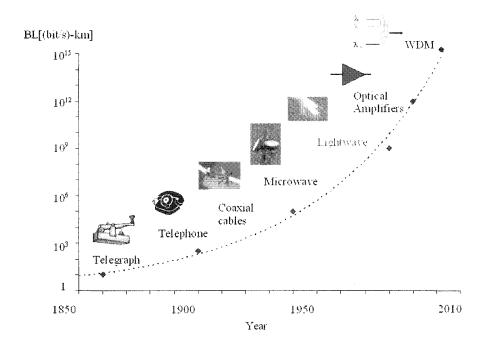

Fibre-optic communication system has become the backbone behind the Internet due to the huge capacity it offers. As the demand for network capacity is growing rapidly, there is an increasing need for all optical based systems capable of offering a much greater bandwidth than the widely used traditional copper cables and RF based communications technologies. A common way to calculate merit of any communication system is the bit-rate-distance product (BL), where B is the bit-rate and L is the repeater spacing, see Figure 1.1. Optical fibre network was first utilised for a simple point-to-point link with no routing capabilities. The second generation systems such as synchronous optical network (SONET) and synchronous digital hierarchy (SDH) [1, 2] employing wavelength division multiplexing (WDM) [3-6] were developed for high speed links with some switching and routing capabilities. Optical add/drop multiplexers (OADMs) and optical crossconnects (OXCs) were developed and exploited to offer wavelength routing in all-optical domain [7]. However, in all conventional communication networks the switching process (i.e. routing packet etc.) is still performed in the electrical domain requiring the costly optical/electrical/optical (O/E/O) conversion modules [7, 8]. Inclusion of O/E/O conversion modules not only requires additional power, but it also imposes bandwidth bottleneck largely due to the processing speed of the conventional electronic components currently being limited to 40 Gbit/s [9, 10]. Although the electronic processing speed is increasing and in the next few yeas 80 Gb/s may be practically realizable, there is a growing research interest to ensure that the next generation optical networks are all-optical with no O/E/O conversions at all [11-15]. This is a challenge that a number of researchers have addressed over that last few years, and as a results we are now seeing practical implementation of all-optical networks at speeds far beyond the most advanced O/E/O devices [16]. Of course, the penalty paid for this surge in speed is the cost and complexity of the network. However, with large scale deployment of all-optical systems, it is expected that the cost will drop considerably, thus making it viable for a large scale adaptation at a global level.

Figure 1.1 BL products against the different communication technologies

All-optical networks based on packet-switching [17-23] are more flexible compared with the traditional circuit-switched networks thus offering bursty traffic as well as higher throughput and switching speed [23, 24]. An all-optical network also offers *transparency* [25] which implies that data can be carried at a mixture of bit rates and protocols, thus the optical layer is capable of supporting different higher layers at the same time.

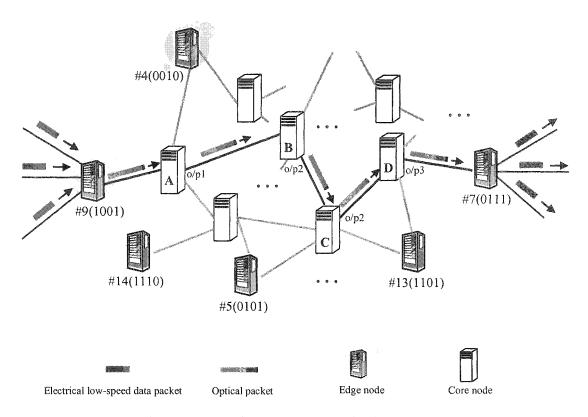

Figure 1.2 illustrates a typical optical core network where optical packets traverse a number of different nodes to reach their intended destination nodes. Packets are composed of payload (information) and a header which contains the destination address. At each node, packet routing decision is carried out by comparing the packet header address with the node identification located in the routing table (RT). If the packet header address matches the node address then the packet is doped otherwise it is passed on to the next stage.

There are a number of packet header recognition and processing techniques that have been developed in recent years [22, 26-28] including the self-routing [29, 30] and the codeword matching [31-33]. Self-routing is the most simplest scheme where, at each node, the packet header address bit sequence extracted are directly used as the control signal to route the packet to the relevant output port of the optical switch (OS). For a larger size network, packets will normally require a longer header field, thus resulting in increased system complexity. In [29], a self-routing scheme that identifies the network nodes output ports instead of the output ports of the nodes themselves has been proposed. This scheme is applicable to networks with arbitrary topologies. It only requires a single-bit processing and allows multiple addresses for the same nodes. By sharing address bits, it is possible to reduce the packet address length by up to 80%. However, self-routing schemes are only suitable for small or medium size networks, since the header length is noticeably expanded as the number of nodes increases.

Figure 1.2 An optical core network with 16 edge nodes

At present, nearly all optical header recognition and processing schemes are based on the packet header address correlation requiring a large size routing table (> 5×10<sup>5</sup> entries) [34, 35]. In [31-33], all-optical bank correlators, and all-optical logic circuits have been employed, respectively to implement all-optical codeword matching in small-scale networks with a routing table of many entries. However, for larger-scale networks, the implementation of the above schemes would be a challenging and time consuming task due to complexity of all-optical configurations, a large size routing table and lack of all-optical storage. For a small size network (i.e. reduced size routing table) header processing could be implemented using a bank of all-optical mirror-based correlators [31] and all-optical logic gates (OR, XOR, AND) [36-53]. However, for a larger size network, the correlation becomes a challenging task due to the exponential increase in the number of routing table entries. In addition, all-optical

logic gates employing active nonlinear devices such as the semiconductor optical amplifiers (SOAs) [54-57] suffer from a long gain recovery time (~ 1 ns) after each correlation, thus limiting the operational speed to 80 Gb/s. Therefore, to carry out a large number of correlation at high data rates (> 80 Gb/s) in the optical domain with a minimum processing time, one desires to utilise either a significant number of parallel gates or a small number of gates for sequential correlation. However, these solutions are not feasible in the current practical systems.

An alternative packet header processing method based on the pulse-positionmodulation based header processing (PPM-HP) has been proposed in [58, 59]. In this scheme both the incoming packet header address bits and the routing table entries are converted from return-to-zero format into a PPM format. The advantages of this scheme are (i) significantly reduced routing table entries, where each entry contains more than one header address information in the form of a PPM pulse, (ii) considerably reduced correlation processing time by using only a single bitwise AND gate instead of a large number of gates with a low response-time, and (iii) offering multiple transmitting modes (unicast, multi-cast and broadcast) embedded in the optical layer. The conventional PPM router requires a serial-to-parallel converter (SPC) to extract the individual bits from the incoming packet header address, an array of 1×2 switches and the delay lines. For packets with a long header address sequence, the switching stages at the header address conversion module will contribute to the deterioration of the extinction ratio of the output PPM address and increased system complexity. In CHAPTER 4, an enhanced node architecture based on the PPM address format no longer employing SPC and an array of 1×2 switches has been proposed, thus significantly reducing the system complexity.

The processing time of the conventional PPM router is limited by the length of the PPM address time frame (i.e. the entry length of the PPM routing table). In CHAPTER 5, a new routing scheme based on the multiple pulse position routing tables (multiple PPRTs) has been proposed, where by checking the most significant bits (MSBs) of the packet address, only a subset of the header address is converted into a PPM format, thus resulting in a reduced length of PPRT entries leading to significantly reducing router's processing time. A simplified and efficient routing scheme based on a hybrid header address has been proposed in CHAPTER 6, where the packet header address is based on the binary and the PPM formats. The hybrid address correlation scheme employing multiple PPRTs offers improved processing time and reduced system complexity. The abovementioned PPM routers are only designed for routing packets at a single wavelength. To increase the network throughput, an all-optical router based on the PPM correlation capable of routing WDM packets at multiple wavelengths simultaneously is presented in CHAPTER 7.

#### 1.2 Aims and Objectives

This PhD research work aims to investigate the three main issues in all-optical routing scheme:

#### All-optical ultrafast header processing and address correlation

Investigate the current and future trends of all-optical header processing and address correlation schemes in all-optical networks (above 80 Gb/s). The node complexity is reduced by adopting the PPM formatted packet header address, and address correlation time is significantly improved by reducing the size of the routing table. To achieve this, the followings have been carried out:

- · Defined new optical packet profile, node architecture

- Considerably reduced numbers of all-optical correlators

- Designed an optical logic for address correlation

- Carried out full-analysis of the node architecture and complete simulations of multi-hop routing

- Carried out system analysis (crosstalk, etc.)

- Compared analytical and simulated results

#### All-optical component

Investigate and analyse all-optical components, such as all-optical serial-to-parallel converter, all-optical switches with a high extinction ratio, and all-optical logic gates.

## 1.3 Chapter Outline

The thesis is organised into eight chapters as outlined below:

**CHAPTER 1 - INTRODUCTION:** It presents the research fundamental background and the aims and objectives of the research. It also outlines the original contributions made.

CHAPTER 2 - LITERATURE REVIEW OF ALL-OPTICAL ROUTING SCHEMES AND ALL-OPTICAL SWITCHES: The footprint of optical network evolution is presented in this chapter. All-optical packet-switching routing, address correlation schemes, and all-optical switches used for ultrafast optical processing are also introduced in this chapter.

**CHAPTER 3 - SEMICONDUCTOR AMPLIFIER, SYMMETRIC MACHZEHNDER AND ITS APPLICATIONS:** The structure and the nonlinearities of the SOA, and operation principle of the SMZ (i.e. the building block of the router) are illustrated in this chapter. Besides, a number of all-optical elements such as all-optical 3-input AND gate based on four-wave mixing, all-optical serial-to-parallel converter based on SMZ and an all-optical high contrast ratio 1×2 switch based on the SMZs are first reported and evaluated in simulation.

CHAPTER 4 - PPM BASED PACKET HEADER ADDRESS FORMAT:

Converting a conventional binary address pattern into a PPM format will require a

SPC, an array of 1×2 switches, and a number of fibre delay lines. In this chapter, a

simplified routing scheme with no PPM address conversion modules is presented,

thus offering reduced complexity.

CHAPTER 5 - ULTRA-FAST ALL-OPTICAL PACKET SWITCHED ROUTER WITH MULTIPLE PPRTS: In this chapter, a new routing scheme is proposed to improve the header address correlation time. The length of each PPRT entry is further reduced by introducing a novel multiple PPRT scheme. From the simulation results, therefore, it is shown that the header processing time is also reduced in comparison with the router using a single PPRT.

CHAPTER 6 - ALL-OPTICAL PACKET-SWITCHED ROUTER WITH A

HYBRID HEADER ADDRESS FORMAT: A simplified and efficient routing

scheme based on the hybrid header address is proposed in this chapter, where the

packet header address is based on the binary and PPM formats. The hybrid address correlation scheme employing multiple PPRTs offers improved processing time and reduced system complexity.

CHAPTER 7 - MULTIPLE WAVELENGTH ROUTER FOR WDM SYSTEM:

In this chapter, a router designed for WDM optical transmission system capable of simultaneously routing packets at multiple wavelengths with no wavelength conversion modules is outlined. At the input of the router, packets at multiple-wavelengths are fed into a bank of PPM-HP modules via a WDM demultiplexer. Packets at specific wavelengths are processed at the PPM-HP modules.

CHAPTER 8 - CONCLUSIONS AND FUTURE: A summary of the research work is presented in this final chapter. The key findings and the comparisons of different proposed routing schemes will be outlined. The proposed further research directions and the challenges of realising all-optical packet-switched networks will be also discussed in the last chapter.

### 1.4 Original Contribution

Contributions to the knowledge of this research work are as follows:

Proposed and investigated an enhanced PPM router architecture based on the

PPM address format, which significantly reduces the system complexity

compared with the previous PPM routing scheme, see CHAPTER 4.

- Proposed a new routing scheme based on the multiple pulse-position routing tables, resulting in significantly reduced header address correlation time, see

CHAPTER 5.

- Proposed a simplified and efficient routing scheme based on packets with a hybrid address. The new routing scheme employing multiple PPRTs offers faster processing time and reduced system complexity, see CHAPTER 6.

- Proposed a new WDM router architecture for increasing the system throughput, which requires no wavelength conversion modules thus reducing the system complexity, see CHAPTER 7.

- Investigated the crosstalk characteristics of an all-optical serial-to-parallel converter, see Section 3.4.

- Further improvement of the existing ultrafast optical switches with higher contrast ratio, see Section 3.6. Have proposed a new all-optical 3-input AND gate, see Section 3.7.

The list of publications during this research works are as follows:

#### Articles and Letters in Journals

1. H. Le-Minh, Z. Ghassemlooy, W. P. Ng and M. F. Chiang, "All-optical router with PPM header processing in high speed photonic packet switching networks", accepted by IET Communications.

#### Conference papers

- 1. M. F. Chiang, Z. Ghassemlooy, W. P. Ng, H. Le Minh and V. Nwanafio, "Crosstalk investigation of an all-optical serial-to-parallel converter based on the SMZ", proceeding of the 7th Annual Postgraduate Symposium on the Convergence of Telecommunications, Networking and Broadcasting (PGNET 2006), ISBN: 1-9025-6013-9, pp. 217-221, Liverpool, UK, Jun. 2006.

- 2. H. Le-Minh, Z. Ghassemlooy, W. P. Ng and M. F. Chiang, "All-optical packet router based on multi-wavelength PPM header processing", proceeding of the 11th European Conference on Networks & Optical Communications (NOC 2006), ISBN: 3-923613-40, pp. 360-367, Berlin, Germany, Jul. 2006.

- 3. H. Le-Minh, Z. Ghassemlooy, W. P. Ng and M. F. Chiang, "Simulations of alloptical multiple-input AND-gate based on four wave mixing in a single semiconductor optical amplifier", proceeding of the 14th IEEE International Conferences on Telecommunications 2007 (ICT-MICC 2007), ISBN: 978-1-4244-1094-1, pp. 191-196, Malaysia, May 2007.

- 4. M. F. Chiang, Z. Ghassemlooy, H. Le-Minh and W. P. Ng, "All-optical packet-switched routing based on pulse-position-modulated header", *proceeding of the 7th IASTED International Conferences on Wireless and Optical Communications (WOC 2007)*, ISBN: 978-0-88986-659-1, pp. 291-296, Montreal, Canada, May-Jun. 2007.

- 5. H. Le-Minh, Z. Ghassemlooy, W. P. Ng and M. F. Chiang, "Bit error rate performance of multiple-channel OTDM demultiplexer employing a chained symmetric Mach-Zehnder switch", proceeding of the 50th IEEE Global Telecommunication Conference (GLOBECOM 2007), ISBN: 978-1-4244-1043-9, pp. F07P05, Washington DC, USA, Nov.-Dec. 2007.

- 6. M. F. Chiang, Z. Ghassemlooy, W. P. Ng and H. Le-Minh, "Simulation of an all-optical 1×2 SMZ switch with a high contrast ratio", proceeding of the 8th Annual PostGraduate Symposium on the Convergence of Telecommunications, Networking

- and Broadcasting (PGNET 2007), ISBN: 1-9025-6016-7, pp. 65-69, Liverpool, UK, Jun. 2007.

- 7. M. F. Chiang, Z. Ghassemlooy, W. P. Ng and H. Le-Minh, "Ultra-fast all-optical packet-switched router with multiple pulse position routing tables", *proceeding of the 12th European Conference on Networks & Optical Communications (NOC 2007)*, ISBN: 978-91-633-0869-7, pp. 571-578, Kista Stockholm, Sweden, Jun. 2007.

- 8. M. F. Chiang, Z. Ghassemlooy, W. P. Ng, H. Le-Minh, and A. Abd El Aziz: "Multiple-hop routing in ultra-fast all-optical packet switching network using multiple PPM routing tables", *proceeding of IEEE International Conference on Communications 2008 (ICC 2008)*, ISBN: 978-1-4244-2075-9, pp. 5231-5325, Beijing, China, May. 2008.

- 9. M. F. Chiang, Z. Ghassemlooy, W. P. Ng, H. Le-Minh, and A. Abd El Aziz: "An ultrafast 1×M all-optical WDM packet-switched router based on the PPM header address", *proceeding of ICEE 2008*, Paper No. 2631, Tehran, Iran, May. 2008.

- 10. M. F. Chiang, Z. Ghassemlooy, W. P. Ng, H. Le Minh, and C. Lu: "Ultra-fast alloptical packet-switched routing with a hybrid header address correlation scheme", proceeding of IEEE International Conference on High Performance Switching and Routing 2008 (HPSR 2008), ISBN: 978-1-4244-1982-1, pp. 92-97, Shanghai, China, May. 2008.

- 11. M. F. Chiang, Z. Ghassemlooy, W. P. Ng, and H. Le Minh, "Simulation of an alloptical 1×2 SMZ switch with a high contrast ratio", proceeding of the 6th Symposium on Communication Systems, Networks and Digital Signal Processing 2008 (CSNDSP 2008), ISBN: 978-1-4244-1876-3, pp. 475-478, Graz, Austria, July 2008.

- 12. A. Abd El Aziz, Z. Ghassemlooy, W. P. Ng and M. F. Chiang, "Optimisation of the key SOA parameters for amplification and switching", proceeding of the 9th Annual PostGraduate Symposium on the Convergence of Telecommunications, Networking and Broadcasting (PGNET 2008), ISBN: 978-1-902560-19-9, pp. 107-111, Liverpool, UK, Jun. 2008.

#### **Posters**

- 1. M. F. Chiang, Z. Ghassemlooy, W. P. Ng and H. Le-Minh, "Future Ultra-high speed Optical Networks: Optical Router based on Slotted-Time-Domain Processing" Booklet of Presentations in 2006 of *Britain's Top Early-Stage Engineers on UK Engineering Research and R&D at the House of Commons (Poster presentation for SET for BRITAIN 2006)*, pp. 14, London, UK, Dec. 2006.

- 2. M. F. Chiang, Z. Ghassemlooy, W. P. Ng and H. Le-Minh, "Ultrafast all-optical packet-switched router", *UK GRAD Programme Yorkshire & North East Hub, Poster Competition & Network Event*, Leeds, 9 May 2007, Poster No. 15.

- 3. M. F. Chiang, Z. Ghassemlooy, W. P. Ng and H. Le-Minh, "Ultrafast all-optical packet-switched router", *Northumbria University, CEIS, annual research forum* 2008.

# CHAPTER 2 LITERATURE REVIEW OF ALL-OPTICAL ROUTING SCHEMES AND ALL-OPTICAL SWITCHES

#### 2.1 Introduction

Optical fibre is an ideal transmission media for light due to its low power attenuation [60]. However, as optical signals travel through the fibre, there are several impairment factors which distort the signal quality due to the fibre characteristics, such as intermodal dispersion [61], chromatic dispersion [62], polarisation mode dispersion [63] and fibre nonlinearities [64]. Other factors generated by the optical devices, such as the accumulated noise [65], crosstalk [66, 67] also deteriorate the system performance, thus limiting the total throughput of the optical network. Crosstalk (CXT) can be classified into inter-channel CXT and intra-channel CXT: the former one denotes that the undesired signal is at a different wavelength from the desired signal. The later one happens when the undesired and desired signals are at the same wavelength [62]. In order to achieve a low loss and high bit-rate long distance transmission link, each network generation has brought about a fundamental breakthrough and noticeable improvement in system performance. In this chapter, the evolution and topologies of optical network are introduced in Sections 2.2 and 2.3, respectively. The basic architecture of an all-optical packet switching core router and different header recognition scheme are illustrated in Section 2.4. A number of optical switches and all-optical switches are outlined in Sections 2.5 and 2.6, respectively. Finally, Section 2.7 will conclude this chapter.

#### 2.2 Evolution of Optical Network

Fibre-optic communication systems have been deployed worldwide since 1980 and constitute the backbone behind the Internet. A breakthrough came about in 1970s with the developed of compact optical source and low-loss fibres. Following this, terrestrial lightwave systems became commercially available from 1980 onwards. The 1st generation optical systems (networks) developed in 1970s adopted the operation wavelength of 800 nm (known as the 1st window) and used GaAs semiconductor laser and a PIN photodiode as an optical source and receiver, respectively. The bit-rate offered was ~45 Mb/s with a repeater spacing of up to 10 km, far higher than what could have been achieved with the copper cable or radio frequency (RF) based transmission systems [68]. 2<sup>nd</sup> generation systems were introduced in 1980s where the operation wavelength was shifted to ~1300 nm, where optical fibre exhibits the minimum dispersion and fibre losses are below 0.5 dB/km [69, 70]. It offered higher bit-rates of 100 Mb/s and 1.7 Gb/s with multi-mode fibre and of sing-mode fibre (SMF) with a repeater spacing of about 50 km, respectively [60]. The system based on SMF deployed in 1980 is still forming the worldwide fibre based backbone network. It will take some time before the fibres will be replaced with those operating at higher wavelengths.

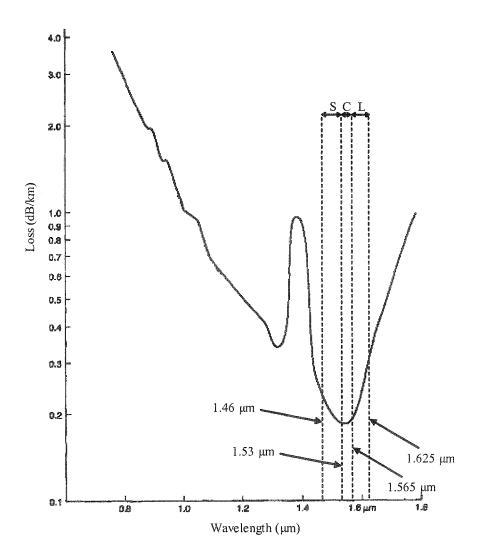

The 3<sup>rd</sup> generation systems came about in late 1980s that adopted operating wavelength of 1550 nm where optical fibre display the minimum loss of 0.2 dB/km but with slightly higher dispersion compared with the 1300 nm wavelength [60, 62]. Using dispersion compensating fibre (DCF) together with the distributed-feedback (DFB) semiconductor laser sources bit-rate in excess of 10 Gb/s with a repeater spacing of about 60~70 km were achieved [60]. 4<sup>th</sup> generation introduced in early

1990s saw the development and deployment of WDM based technology capable of offering increased total capacity in the orders of magnitudes. The main breakthrough came about by the development of erbium-doped fibre amplifier (EDFA) which made it possible amplification at 1550 nm window, thus being able to transmit high speed data over a long fibre span [60, 71]. In 2003, 373 channels each operating at 10 Gb/s were transmitted over 11000 km of SMF offering a *BL* product of 41000 (Tb/s)-km, a magnificent achievement since the early days of optical fibre communications [60].

$5^{th}$  generation introduced in early 2000 show an increase in the number of wavelengths, thus leading to creation of three new bands: C-band (1530  $\sim$  1565 nm), as well as L-band (1565  $\sim$  1625 nm) and S-band (1460  $\sim$  1530 nm), see Figure 2.1 [72]. Raman based optical amplifiers [73, 74] were readopted since EDFAs are not cable to operate at such a wide spectral band.

WDM technology first introduced in 1980 and became commercially available in 1995 [6, 25, 75]. The enormous capacity of the WDM systems is achieved by having a very narrow channel spacing of 0.4 nm (50 GHz) or less. In principle, the capacity of a SMF is >30 Tb/s [60, 76], therefore a large number wavelength could be used provided the channel spacing is kept to a minimum as well as the gain of optical amplifier is flat across all wavelength. However, in practical system the minimum channel spacing is limited by the inter-channel crosstalk and by the amplifier gain response [60, 76]. Basically, WDM systems are often classified as coarse or dense systems, depending on their channel spacing (typically, channel spacing of > 5 nm and <1 nm for coarse and dense WDM systems, respectively [60]. In most commercially available WDM systems channel spacing is 100 GHz (0.8 nm at 1552)

nm [60, 77]. Recently, the International Telecommunication Union (ITU) has specified narrower channel spacing of 25 and 50 GHz for future WDM systems [25, 62].

Figure 2.1 Fibre loss (dB/km) versus wavelength ( $\mu m$ )

# 2.3 Optical Network Topologies

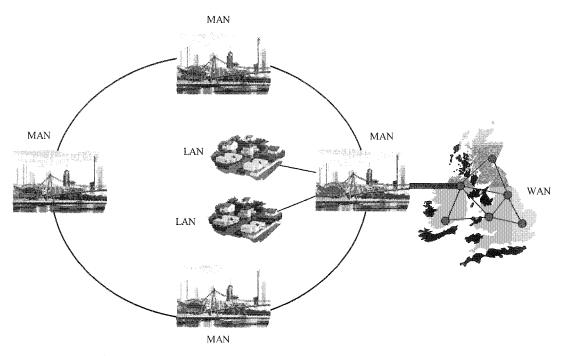

Optical networks can be divided into three groups depending on the area they cover, see Figure 2.2:

- Local-area network (LANs): In LANs, the transmission distance are short such as a campus or a town (normally < 10 km), therefore the fibre losses [60], dispersions [62, 63] and nonlinear effects [64] are not major issues [60]. LANs is often called the access network and is the most closest to the end-users [78].

- Metropolitan-area networks (MANs): MANs interconnects with a number of LANs in big cities. Typically, a ring topology is used in MANs to connect with WANs by the edge nodes (or egress nodes) [60, 79, 80].

- Wide-area networks (WANs): WANs cover a large area such a country or a continent, and are often called as transports networks or core networks [60, 81], where routers (or nodes) in the core networks are located in large metropolitan areas.

Figure 2.2 A typical optical network showing LAN, MAN, and WAN

In today's optical transport networks, synchronous digital hierarchy/synchronous optical networks (SDH/SONET) are the most important optical standards, the switching processes in SDH/SONET are performed in the electrical domain, which can be slow. SHD/SONET was designed to carry several former digital transmission standard, such as plesiochronous digital hierarchy (PDH) [82] and asynchronous transfer mode (ATM) [83-85]. SONET is used in USA and Canada only, the basic operation bit-rate is 155.52 Mb/s, which is also standardised as synchronous transport module – 1 (STM-1). Nevertheless, SDH is used in rest of the world with a basic operation bit-rate of 51.84 Mb/s (i.e. one third of STM-1), which is also standardised as synchronous transport signal - 1 (STS-1). In STS-1, a frame is 810 octets in size. Each frame is transmitted as 3 octet of overhead followed by 89 octets of payload. This transmission process is repeated nine times until a complete frame is transmitted (i.e. 810 octets) in 125 ms [86, 87].

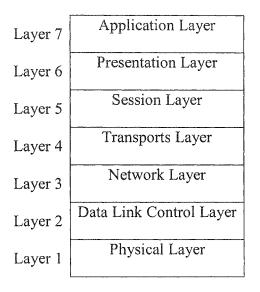

Optical transport networks such as SDH and SONET are associated with the open system interconnection (OSI) layer 1, see Figure 2.3. The physical layer (i.e. layer 1)

consists of a number of optical components including fibres, transmitters, fibres, amplifiers, and receivers [60, 88].

Figure 2.3 The OSI model

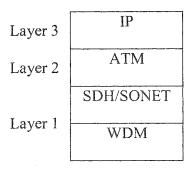

Figure 2.4 shows the network architecture of telecommunication system. Typically, the Internet protocol (IP) packets [89-91] sent by the end-users are converted to ATM cells [83-85] before being applied to SDH/SONET transportation circuit and to the backbone WDM systems. Packet over SDH/SONET (PoS) is an alternative scheme for routing IP packets, where IP packets are directly packed into SDH/SONET with no ATM layer at all.

Figure 2.4 The telecommunication core networks architecture [60]

In optical networks to deliver the data across the network to its destination, a number of switching techniques have been proposed as outlined below.

Optical circuit switching (OCS): Currently used SDH/SONET networks are based on circuit switching which are more suitable for voice and real-time traffic [60, 92]. The main advantage of employing OCS is that it uses simple processing and buffering schemes. However the data traffic being the dominant traffic is not optimised for circuit switching [93]. Wavelength routing technology [60, 94] is based on OCS and is currently used in the WDM network, the incoming data at a specific wavelength can be switched to its corresponding output by using OXCs. Although the point-to-point connection is simple, the fibre capacity is not used efficiently. In the wavelength routing, the connection for each hop is established by using a wavelength, called lightpaht [95, 96]. Because the capacity is fixed in one lightpath, therefore, the resource becomes wasteful while only carrying a small amount of data [97].

Optical code division multiplexing (OCDM) switching: In OCDM switching, routing information is coded by transmitting a series of short pulses named chips within a bit duration. Each switching node is assigned a unique code with "chips". Only a data with the same code can be decode by the unique switching node, the rest of data with different codes will be considered as "noise" to this specific node [98-100]. Basically, there are two methods in OCDM switching: OCDM-label switching and OCDM-path switching. In OCDM-label switching, the routing information is carried by an optical-encoded label at the head of the payload data. In OCDM-path switching, the routing information is carried by the data bits themselves, each individual data bit is optically encoded, this manner is very similar to the wavelength

routing [60, 94], but the routing information is carried by the optical code rather than the wavelength [97].

Optical burst switching (OBS): OBS is a compromise to achieving a truly "transparent" optical packet switching. In OBS, many packets are combined into a single burst, and the data and control signals are transmitted on different channel, with the control signals being processed electronically [8, 101, 102]. There are mainly three different methods for transmitting the control signals: Tell-and-wait (TAW), tell-and-go (TAG), and just-enough-time (JET). In TAW scheme [103-105], the source node transmits the control packet first, and waits for the response message from next node, then sends the burst data. In TAG scheme [103-105], the source node transmits the control packet first and immediately transmits the optical burst without waiting for response from next node. In JET scheme [103-105], there is a time delay between the transmission of the control packet and the optical burst data.

Optical packet switching (OPS): OPS is considered as the most desirable switching technique for the next-generation optical network. It is aimed to offer a better efficient utilisation of huge bandwidth providing by fibre. In OPS, fast routing is achievable by employing all-optical switches and all-optical signal processing techniques [24, 62]. However, the main issue in OPS is the lack of optical memory for buffering. Packet header recognition and processing are required in each switching node, thus increasing the node complexity [13, 18, 79, 106-108].

# 2.4 All-optical Packet Switching Core Router and Header Recognition Scheme

All-optical packet-switched networks are aimed to offer networks with fast switching [109] and more flexible utilisation of the optical bandwidth[62, 110]. However, in order to achieve a truly all-optical packet-switched network, all-optical header processing and address correlation are required at every router. In this section, the basic optical packet format and the fundamental router architecture are illustrated. Several different approaches for optical packet header processing are also introduced in this section.

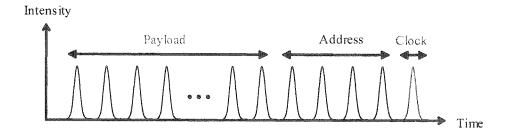

#### 2.4.1 All-optical packet switching core-router

Optical packets across the core network are assembled by the edge router from MANs. Typically, an optical packet is composed of three parts: the clock, the address and the payload, see Figure 2.5. Clock signal is used for synchronising the timing within a router, and the address information is employed for labelling packet destination. The payload is the real information, which is composed of slow-speed packets having the same destination. Optical packets are delivered from one node to another across the optical core network until reaching their destination nodes, see Figure 1.2. The node/router delivers the packets to different routs based on the information extracted from the packet address.

Figure 2.5 A typical format of an optical packet

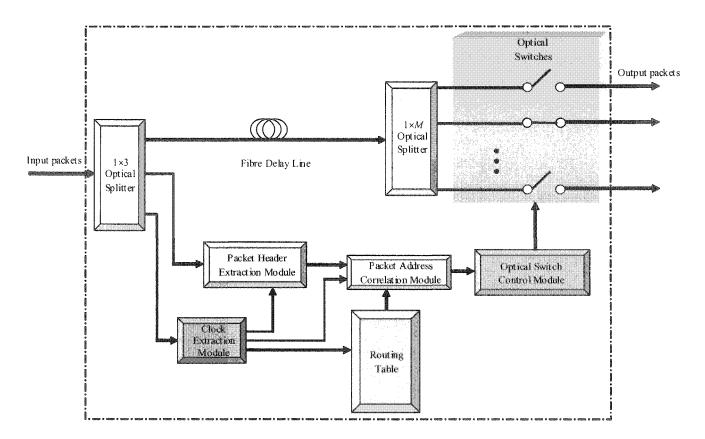

Figure 2.6 shows the fundamental architecture of a core router in an all-optical packet-switched network. Basically, the router is composed of a number of key modules, such as the clock extraction module for synchronisation, the packet header extraction module for retrieving packet destination, a routing table for storing the routing information (i.e. the shortest path through a number of core routers to its destination), the packet address correlation module for comparing the packet address and routing table thus making the routing decision, the optical switch control module for controlling the optical switches, and optical switches for switching the input packets. There are other optical modules (not shown in the figure) such as reshaping and re-amplification (2R) [111-115] and reshaping, re-amplification and retiming (3R) [116-121] regenerators and optical buffering module [9, 109, 122-128].

Figure 2.6 A block diagram of an optical packet-switched router architecture

In any network, contention is an issue, which happens when more than one packet are switched to the same output port at the same time. There are three schemes to solve packet contention problem: Optical buffering, deflection routing and wavelength conversion.

Optical Buffering: In traditional electrical packet switching, buffering can be easily achieved by using electrical random-access memory (RAM). However, this is not easily possible in optical domain, there is no optical RAM nowadays. Typically, optical buffers are implemented by using Fibre Delay Lines (FDL). FDL is an easy way to achieve buffering, however it is not flexible enough. This is because FDL does not have random access capability, thus packets can be retrieved only after it is passed through a specific length of fibre. Additionally, a long length of fibre is needed to achieve a short delay time (1 μs delay with 200 m of fibre) [106].

**Deflection Routing:** By means of forwarding the contention packets to different paths. However, using alternative path usually results in more propagation delay (i.e. require to travel a longer path to its destination) [129-131]. Deflection routing may also result in forwarded packets still circulating within the network, thus requiring more sophisticated protocols to avoid this [106].

Wavelength Conversion: When two packets try to leave an output port at the same time, one of them can be converted to a different wavelength by using a Wavelength Converter (WC) [11, 132-140]. This approach is the most efficient way because it does not delay the signals or use deflection routing [106]. However it requires large numbers of WCs with low noise figures and high extinction ratios, thus maintaining the original bit rates, data format, polarisation, and power.

#### 2.4.2 Packet header and header recognition