# Northumbria Research Link

Citation: Wang, Xiang, Wu, Haimeng and Pickert, Volker (2021) Phenomenon of Short-Time Threshold Voltage Shift and Its Application in Junction Temperature Estimation. In: 2021 IEEE 1st International Power Electronics and Application Symposium (PEAS). IEEE, Piscataway, US, p. 9628403. ISBN 9781665413619, 9781665413596, 9781665413602

Published by: IEEE

URL: https://doi.org/10.1109/PEAS53589.2021.9628403 <a href="https://doi.org/10.1109/PEAS53589.2021.9628403">https://doi.org/10.1109/PEAS53589.2021.9628403</a>

This version was downloaded from Northumbria Research Link: http://nrl.northumbria.ac.uk/id/eprint/47250/

Northumbria University has developed Northumbria Research Link (NRL) to enable users to access the University's research output. Copyright © and moral rights for items on NRL are retained by the individual author(s) and/or other copyright owners. Single copies of full items can be reproduced, displayed or performed, and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided the authors, title and full bibliographic details are given, as well as a hyperlink and/or URL to the original metadata page. The content must not be changed in any way. Full items must not be sold commercially in any format or medium without formal permission of the copyright holder. The full policy is available online: <a href="http://nrl.northumbria.ac.uk/policies.html">http://nrl.northumbria.ac.uk/policies.html</a>

This document may differ from the final, published version of the research and has been made available online in accordance with publisher policies. To read and/or cite from the published version of the research, please visit the publisher's website (a subscription may be required.)

# Phenomenon of Short-Time Threshold Voltage Shift

# and Its Application in Junction Temperature

## Estimation

Xiang Wang

School of Engineering

Newcastle University

the United Kingdom

x.wang108@newcastle.ac.uk

Haimeng Wu

Department of Mathematics, Physics &

Electrical Engineering

Northumbria University

the United Kingdom

haimeng.wu@northumbria.ac.uk

Volker Pickert

School of Engineering

Newcastle University

the United Kingdom

volker.pickert@newcastle.ac.uk

Abstract-Silicon carbide (SiC) has seen tremendous advancement in high-efficiency, high-frequency, and hightemperature applications during recent years. However, the gate oxide of SiC MOSFET is reported to be less reliable compared with its Si counterpart, introducing the problem of threshold voltage  $(V_{th})$  shift. Recent publications have investigated  $V_{th}$  shift which are mainly based on the long-time scale ranging from seconds to several days. However, the  $V_{\rm th}$ shift in a shorter time scale has not been widely discussed and studied due to its high bandwidth requirement in measurement. This paper proposed an investigation into the short-time  $V_{\rm th}$ shift using a developed current-controlled gate driver. The phenomenon of short-time  $V_{th}$  shift is captured and analyzed, which shows that it occurs within the first microsecond of the gate voltage being applied. Moreover, a modelling approach using the logarithm equation is proposed to describe the relationship between the short-time  $V_{th}$  shift and the gate stress time. Experiments are conducted under different temperatures, illustrating the temperature dependency of the short-time  $V_{\rm th}$ shift process.

Keywords—SiC MOSFET, threshold voltage, V<sub>th</sub> shift, TSEP

### I. INTRODUCTION

In recent years, Silicon carbide (SiC) has experienced rapid development gaining an increasing widespread use in high-efficiency, high-frequency, and high-temperature applications [1]. As a potent alternative to current silicon (Si) technology, SiC power electronics shows superior characteristics such as higher voltage ratings, lower voltage drops, faster switching speeds, and higher thermal conductivities[1]. Among all the SiC switches (e.g. SiC BJTs, JFETs, MOSFETs and IGBTs), the SiC MOSFET has become the most prevalent switch in the recent 2-10 years[2][3]. However, recent publications show that SiC MOSFET have less reliable gate oxide performance [4], [5]. It is well known that the threshold voltage  $(V_{\mathrm{th}})$  is an important parameter to estimate the health condition of a MOSFET[6] and the shift of  $V_{\rm th}$  has been investigated in various publications [7][8], which reveals a close relationship between the  $V_{th}$  and the gate stress time. On the other hand, the experiments are all conducted in the time scale over seconds which do not cover the study of the short-time  $V_{\rm th}$  shift issue that is at switching periods. The phenomenon of short-time  $V_{\rm th}$  shift is difficult to observe because of the requirement for high bandwidth sampling circuit in the measurement. This paper presents an investigation into the shot-time  $V_{\rm th}$  shift with a new measurement method using a developed current-controlled gate driver. It is shown that the short-time  $V_{th}$  shift introduces

This project is supported by Engineering and Physical Sciences Research Council (EPSRC) project (EP/R004366/1), Newcastle University and China Scholarship Council (CSC).

the dissimilarity between experiment and simulation. Moreover, the investigation into short-time  $V_{\rm th}$  shift can provide an a new angle for the gate oxide degradation mechanism. New parameters that are contained in the short-time  $V_{\rm th}$  shift process can be used for the area of health condition monitoring.

#### II. MECHANISM OF $V_{\text{TH}}$ SHIFT

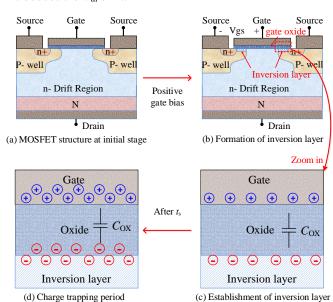

$V_{\rm th}$  shift is generally regarded as the results of gate charges trapped in the gate oxide defects. Fig. 1 shows the establishing process of  $V_{\rm th}$  shift, including the MOSFET structure, formation of the inversion layer, establishment of the inversion layer and the charge trapping period in oxide which introduces the  $V_{\rm th}$  shift.

Fig. 1. V<sub>th</sub> shift mechanism: (a) MOSFET structure at initial stage; (b) Formation of inversion layer; (c) Establishment of inversion layer; (d) Charge trapping period.

The initial structure of MOSFET is shown in Fig. 1(a) without applying gate bias. When a positive gate bias ( $V_{\rm gs}$ ) is applied across the gate and source terminals and  $V_{\rm gs}$  is higher than  $V_{\rm th}$ , the inversion layer is formed beneath the gate oxide as shown in Fig. 1(b). The established structure of the inversion layer is demonstrated in Fig. 1(c). The inversion layer is formed by electrons gathering beneath the gate oxide due to the gate bias voltage. The gate charges ( $Q_{\rm g}$ ) can be determined by the gate voltage with the equation  $Q_{\rm g} = V_{\rm gs} \cdot C_{\rm OX}$ , where  $C_{\rm OX}$  is the gate capacitance. After the stress time  $t_{\rm s}$ ,

some of the electrons are trapped by the defects inside the oxide, as shown in Fig. 1(d). These trapped charges can no longer move from source to drain. However, the number of charges to form the inversion layer is not changed. Therefore, more charges are needed to conduct the same current, resulting in the positive shift of  $V_{\rm th}$ . The shift of  $V_{\rm th}$  reflects the number of charges trapped inside the oxide. The negative Vth shift is a similar process when the electrons inside the defects of the oxide are dragged out under negative gate bias. The shift of  $V_{\rm th}$  may introduce the breakdown of the gate oxide. When more charges are trapped inside the gate oxide, the electrical field in the gate oxide increases as the distance is narrowed between the gate terminal and the electrons. Therefore, the estimation of  $V_{\rm th}$  shift is an important parameter to reflect the health condition of the MOSFET.

#### III. PHNOMENON OF SHORT-TIME $V_{\text{TH}}$ SHIFT

The conventional  $V_{\rm th}$  shift test consists of 3 steps: firstly, the initial  $V_{\rm th}$  is measured before the gate stress; next, the device under test is stressed under a gate voltage for a certain period from 1s to hours; Finally, the  $V_{\rm th}$  after the gate stress is measured again. The differences between the  $V_{\rm th}$  before and after the gate stress is regarded as the  $V_{\rm th}$  shift. However, the gate stressed time under investigation is higher than 1s in publications [9][10]. It is difficult to evaluate the short-time  $V_{\rm th}$  shift within 1s, because high bandwidth is require for fast  $V_{\rm th}$  measurement. In this section, a new method is proposed to investigate the short-time  $V_{\rm th}$  shift using a current-source gate driver.

#### A. Principle of the Proposed Measurement Method

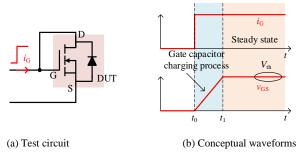

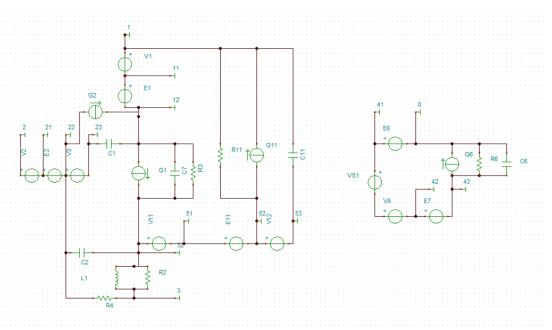

The diagram of the test circuit and the conceptual waveforms are illustrated in Fig.2(a) and Fig.2(b). In the test, the drain and gate terminals of the MOSFET are shorted. A controlled gate current is generated and injected into the gate of the MOSFET as the blue waveform shown in Fig.2(b). The red waveform is the corresponding gate voltage of the MOSFET, which consists of the charging process and the steady state. The charging process is a linear slope, representing the increase of gate voltage on the gate capacitor under a constant current. After the gate voltage reaches the threshold voltage ( $V_{\rm th}$ ) at  $t_{\rm 1}$ , the gate voltage stops increasing and stays at  $V_{\rm th}$ . The behaviour of the gate voltage after  $t_{\rm 1}$  is determined by the short-time  $V_{\rm th}$  shift. In the conventional analysis, the gate voltage keeps unchanged, which can be verified by the simulation.

Fig. 2. Principle of the proposed measurement method: (a) test circuit; (b) conceptual waveforms.

#### B. Simulation Results

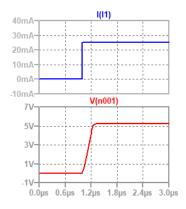

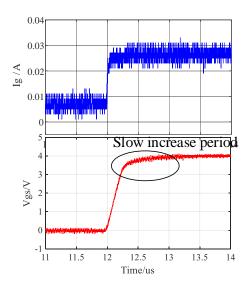

The simulation is conducted to verify the analysis of the proposed measurement method as is shown in Fig.3. The Pspice model used in the simulation is SCT3060 provided by its manufacturer ROHM. A step current signal with a

magnitude of 25mA is injected into the gate terminal of the MOSFET. It is shown that the charging process starts at  $1\mu s$  and the gate voltage stops increasing after  $1.2\mu s$ . The gate voltage then stays at 5.2V after  $1.2\mu s$ , therefore, the simulated  $V_{th}$  is 5.2V. The simulation shows that there is no short-time  $V_{th}$  shift identified in the Pspice model from its manufacturer.

Fig. 3. Simulation result of the proposed measurement method.

#### C. Experiment results

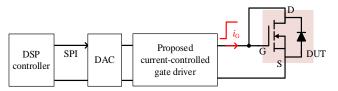

A current-controlled gate driver is designed to investigate the behaviour of the MOSFET via the proposed method. The diagram of the experimental setup is presented in Fig.4. The step current signal is programmed and stored in the DSP controller. The signal is transmitted to a Digital-to-Analog Converter (DAC) via Serial Peripheral Interface (SPI) communication. The step signal is generated by the DAC and input into the current-controlled gate driver to control the gate current of the MOSFET. The details of the gate driver are demonstrated in [8]. It is worth noting that the magnitude of the step current signal can be changed according to the requirement of the test.

Fig. 4. Diagram of the experiment setup.

Fig. 5. Experiment result of the proposed measurement method.

The experiment result is different from the simulation. Fig.5 illustrates the test waveform of the MOSFET under the same condition as the simulation. The device under test is SCT3060, the magnitude of the step current signal is 25mA. Similar to the simulation result, there is also a charging process, where the gate voltage increase linearly in the beginning. However, after the linear increase period, there is a slow increase period, which is not presented in the simulation. Considering that the charging process of the gate capacitor is finished after the linear period, this slow increase period is introduced by the  $V_{\rm th}$  shift.

#### D. Influence of Short-Time V<sub>th</sub> Shift on Switching Transient

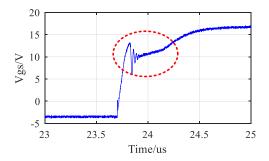

The short-time  $V_{\rm th}$  shift phenomenon is can also be observed from the switching behaviour, which increases Miller plateau of the MOSFET.

Fig.6 shows the turn-on  $v_{\rm gs}$  of SCT3060 at 250V/10A. It is demonstrated that the Miller plateau is not flat but increases slightly, which is different from the expectation of a flat Miller plateau. Comparing the practical result with the simulation waveform shown in Fig.7, it is obvious that the Miller plateau in the simulation is flat while the experiment waveform presents an increasing Miller plateau. The increasing Miller plateau is supposed to be introduced by the short-time  $V_{\rm th}$  shift. This phenomenon also illustrates that the  $V_{\rm th}$  shift happens so fast that it presents influences on the turn-on gate voltage waveform. The influences on the switching loss and other performances require further investigation.

Fig. 6. Experiment waveform of the gate voltage during turn-on transient.

Fig. 7. Simulation waveform of the gate voltage during turn-on transient.

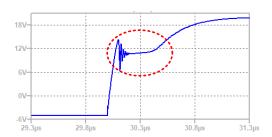

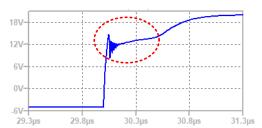

#### E. Modification of Pspice Model

It is stated that the provided Pspice model of the device under test has not included the effect of  $V_{\rm th}$  shift, introducing the difference in the simulation results. By modifying the Pspice model, the simulation can also presents the increasing Miller plateau as shown in Fig.8. The equivalent circuit of the MOSFET can be built based on the code of Pspice model. Fig. 9 demonstrates the modified Pspice model where an additional voltage source VS1 is used to simulate the effect of short-time  $V_{\rm th}$  shift. The equation of the VS1 is presented in the following section. The left part of the circuit is to simulate the output characteristics of the MOSFET, while the right circuit is to simulate the control of the gate signal. The increase on gate voltage is therefore presented in the turn on transient. Simulation is conducted under the same condition as in Fig. 7. Comparing the simulation results before (Fig.7) and after (Fig.8) the simulation, it is shown that the modified Pspice model presents the slow increasing Miller plateau as the experimental results (Fig.6).

Fig. 8. Short-time  $V_{\rm th}$  shift process in a linear time axis.

Fig. 9. Modified equivalent circuit of the MOSFET Pspice model considering short time  $V_{th}$  shift.

## IV. Investigation into Short-Time $V_{\text{th}}$ Shift

### A. Modelling of Short-Time Vth Shift

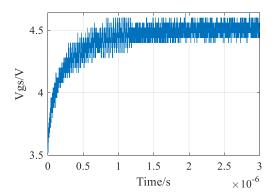

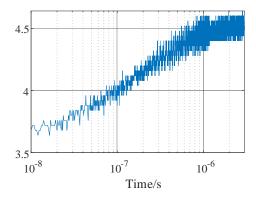

The short-time  $V_{\rm th}$  shift can be modelled using the curve fitting tool. Fig.10 illustrates the zoomed-in details of the slow increase period of the gate voltage when the gate current is 70mA.

Fig. 10. Short-time  $V_{\rm th}$  shift process in a linear time axis.

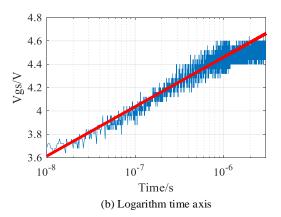

The time interval selected under investigation is the first  $3\mu s$  after the linear increase process. It is shown that the gate voltage increases from 3.5V to 4.5V in the first  $1\mu s$ , and then stays at 4.5V. If the time axis is transformed from the linear axis into the logarithm axis as shown in Fig.11, there is a linear relationship between the short-time  $V_{th}$  shift and the logarithm of time that can be obtained.

Fig. 11. Short-time  $V_{\rm th}$  shift process in a logarithm time axis.

The quantitative relationship can be analyzed using the curve fitting tool. The equation used to model the process is presented in (1):

$$V_{th} = K \cdot \ln t + B \tag{1}$$

where t is the positive bias time of the MOSFET,  $V_{\rm th}$  is the threshold voltage, K and B are two parameters that describe the shifting process. It is worth noting that this model can only describe the shifting process in a certain time range (10ns to 1us). The parameter B represents the initial value, while K reflects the shift speed. A higher K results in a larger shift in the same stressed time.

The experiment waveform is fitted using the equation, the result is shown in (2):

$$V_{th} = 0.184 \cdot \ln t + 7.002 \tag{2}$$

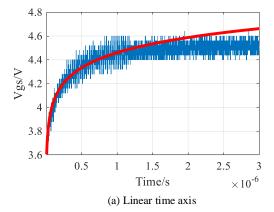

Fig.12 demonstrates the curve fitting results of the proposed logarithm model. The blue waveform is the

measured  $V_{\rm gs}$ , while the red curve is the calculated mathematic relation between  $V_{\rm th}$  and the gate stress time. It is shown that in the first  $1\mu s\ V_{\rm th}$  shifts, the logarithm model can be used to describe the short time shift of  $V_{\rm th}$  under the gate stress.

Fig. 12. Curve fitting result of  $V_{\rm gs}$  in the slow increase period: (a) linear time axis; (b) logarithm time axis.

# B. Short-Time Vth Shift as Temperature Sensitive Electrical Parameters (TSEP)

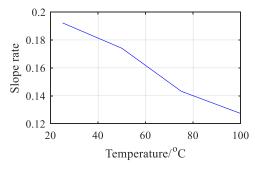

As is stated that the parameter K in equation (1) reflects the shift speed of the short-time  $V_{\rm th}$  shift, which is also the speed for electrons to be trapped inside the oxide in Fig.1(d). The behaviour of electrons is influenced by the temperature, therefore, it is supposed that the parameter K is influenced by temperature.

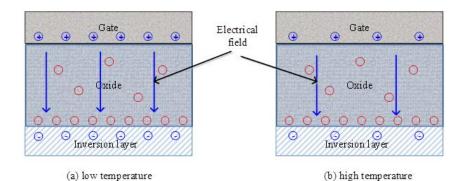

Fig.13 presents the influence of the temperature on the electrical field in the gate oxide. In the condition of higher temperature, the electrons required for the inversion layer are less than at lower temperature [11]-[15]. The decrease of the charges in the inversion layer reduces the electrical field. Therefore, it is expected that the slope rate of the short-time  $V_{\rm th}$  shift is reduced at a higher temperature.

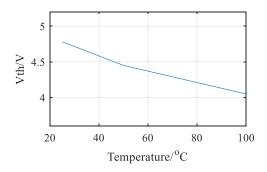

Experiments are conducted under different temperatures to verify the above analysis. The gate current used in the measurement is 70mA. The gate voltage waveforms in different temperature of the device under test are captured and evaluated using the logarithm model. Thereby, the relation between the slope of the short-time  $V_{\rm th}$  shift and the temperature can be obtained, which is presented in Fig. 14. The negative correlation verified the analysis based on the proposed model. It is worth noting that the measured  $V_{\rm th}$  (the gate voltage in the steady state in Fig.2(b).) after short time shift period is reduced from 4.64V to 4.11V along with the

Fig. 13. Influence of temperature on the electrical field in the gate oxide.

increase of temperature as shown in Fig.15. It is concluded that the short-time  $V_{\rm th}$  shift process can be used as an indicator for junction temperature.

Fig. 14. Short-time  $V_{\rm th}$  shift process in a linear time axis.

Fig. 15. Relation between  $V_{\rm th}$  shift and the temperature.

### V. CONCLUSION

This paper provides an investigation into the short-time  $V_{\rm th}$  shift. The test circuit used to observe the short-time  $V_{\rm th}$  shift is presented, whose experimental waveforms illustrate the  $V_{\rm th}$  increase more than 0.5V in 1µs. Also, a Pspice the model of MOSFET has been developed which can reflect the short-time  $V_{\rm th}$  shift effect. This process can be described and quantitated byusing a logarithm equation. In addition, the slope rate of the equation reflects the speed of the short-time  $V_{\rm th}$  shift, which can be used to estimate the junction temperature as a TSEP. At last, the linear relationship of the slope rate and temperature is verified in the experiments.

#### ACKNOWLEDGEMENT

The author thanks the financial support from Engineering and Physical Sciences Research Council (EPSRC) project (EP/R004366/1), Newcastle University and China Scholarship Council (CSC).

## REFERENCES

- J. Rabkowski, D. Peftitsis, and H. Nee, "Silicon Carbide Power Transistors: A New Era in Power Electronics Is Initiated," IEEE Ind. Electron. Mag., vol. 6, no. 2, pp. 17–26, Jun. 2012.

- [2] A. Castellazzi, A. Fayyaz, G. Romano, L. Yang, M. Riccio, and A. Irace, "SiC power MOSFETs performance, robustness and technology maturity," Microelectron. Reliab., vol. 58, no. 5, pp. 164–176, Mar. 2016.

- [3] X. She, A. Q. Huang, O. Lucia, and B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," IEEE Trans. Ind. Electron., vol. 64, no. 10, pp. 8193–8205, 2017.

- [4] A. J. Lelis, R. Green, and D. B. Habersat, "SiC MOSFET threshold-stability issues," Mater. Sci. Semicond. Process., vol. 78, no. August 2017, pp. 32–37, 2018.

- [5] C. T. Yen et al., "Oxide breakdown reliability of sic mosfet," WiPDA Asia 2019 - IEEE Work. Wide Bandgap Power Devices Appl. Asia, pp. 1–3, 2019.

- [6] J. O. Gonzalez, O. Alatise, J. Hu, L. Ran, and P. A. Mawby, "An Investigation of Temperature-Sensitive Electrical Parameters for SiC Power MOSFETs," IEEE Trans. Power Electron., vol. 32, no. 10, pp. 7954–7966, 2017.

- [7] V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," Microelectron. Reliab., vol. 46, no. 1, pp. 1–23, 2006.

- [8] X. Wang, H. Wu, and V. Pickert, "Design of an advanced programmable current-source gate driver for dynamic control of SiC device," Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. -APEC, vol. 2019–March, pp. 1370–1374, 2019.

- [9] C. T. Yen et al., "Oxide breakdown reliability of sic mosfet," WiPDA Asia 2019 - IEEE Work. Wide Bandgap Power Devices Appl. Asia, pp. 1–3, 2019.

- [10] P. Hofstetter, R. W. Maier, and M.-M. Bakran, "Influence of the Threshold Voltage Hysteresis and the Drain Induced Barrier Lowering on the Dynamic Transfer Characteristic of SiC Power MOSFETs," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 944–950.

- [11] S. I. Hayashi and K. Wada, "Accelerated ageing test for gate-oxide degradation in SiC MOSFETs for condition monitoring," Microelectron. Reliab., vol. 114, no. May, p. 113777, 2020.

- [12] X. Lu, V. Pickert, M. Al-Greer, C. Chen, X. Wang, and C. Tsimenidis, "Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals." Energies 14, no. 16 (2021): 4912.

- [13] Z. Weichi, X. Wang, M. Dahidah, G. Thompson, V Pickert, and M. Elgendy. "An Investigation of Gate Voltage Oscillation and Its Suppression for SiC MOSFET." IEEE Access 8 (2020): 127781-127788.

- [14] X. Wang, H. Wu., and V. Pickert, "Gate threshold voltage measurement method for Sic MOSFET with current-source gate driver". In the 10th International Conference on Power Electronics, Machines and Drives (PEMD 2020)(pp. 443 – 447). IET

- [15] X. Wang, H. Wu., and V. Pickert, "A cost-efficient Current-Source Gate Driver for SiC MOSFET Module and its Comparison with Voltage-Source Gate Driver". In 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia) (pp. 979-984). IEEE