# Northumbria Research Link

Citation: Holdsworth, Lee (2001) An investigation into the inherent robustness and optimal harmonic performance of the advanced static var compensator (ASVC). Doctoral thesis, Northumbria University.

This version was downloaded from Northumbria Research Link: https://nrl.northumbria.ac.uk/id/eprint/2144/

Northumbria University has developed Northumbria Research Link (NRL) to enable users to access the University's research output. Copyright © and moral rights for items on NRL are retained by the individual author(s) and/or other copyright owners. Single copies of full items can be reproduced, displayed or performed, and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided the authors, title and full bibliographic details are given, as well as a hyperlink and/or URL to the original metadata page. The content must not be changed in any way. Full items must not be sold commercially in any format or medium without formal permission of the copyright holder. The full policy is available online: <a href="http://nrl.northumbria.ac.uk/policies.html">http://nrl.northumbria.ac.uk/policies.html</a>

Some theses deposited to NRL up to and including 2006 were digitised by the British Library and made available online through the <u>EThOS e-thesis online service</u>. These records were added to NRL to maintain a central record of the University's research theses, as well as still appearing through the British Library's service. For more information about Northumbria University research theses, please visit <u>University Library</u> <u>Online</u>.

# AN INVESTIGATION INTO THE INHERENT ROBUSTNESS AND OPTIMAL HARMONIC PERFORMANCE OF THE ADVANCED STATIC VAR COMPENSATOR (ASVC)

A thesis submitted to

THE UNIVERSITY OF NORTHUMBRIA AT NEWCASTLE

for the degree of

DOCTOR OF PHILOSOPHY

by

LEE HOLDSWORTH

April 2001

### **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification in this or any other university or institution of learning. Dedication

# To Lorraine, Maureen & Sophie

Thank you

### Acknowledgements

I would like to thank all the technical, administrative and academic staff at the University of Northumbria at Newcastle (UNN) for their continuous encouragement and guidance throughout the work. Particularly I would like to thank Dr. Richard Binns, Dr. Li Ran and Dr. Gavin Armstrong for continual academic and technical assistance. Also, I would like to thank Mr. Ed Holmes for his technical assistance in the laboratory.

Gratitude is expressed to my director of studies, Dr. G. A. Putrus. Extensive appreciation is also expressed to the Power Systems research group at UMIST, in particular Professor Nick Jenkins, for allowing time and facilities in the final stages of the work.

For the support and encouragement I have received throughout the project, I would like to thank Adrian Hawkins and James Allen. Also, Dan Joyce for substantial support at times when it was most needed.

Within my family I would like to thank my sister, for giving me strength and determination, my brother for his eccentricity and flair and my dogs (Sophie and Macey) for reminding me of the simplicity of laughter.

Lorraine, a classic novelist could never describe the depth of appreciation and admiration I have for you for helping me through this period of my life. So, as I'm just a simple working class northerner, I'll just say cheers.

Finally to my mother, it may have taken some time but I have eventually realised that it's the love in your life and the smile on your heart that's the true measure of the achievement in your life. So open your heart and smile on you crazy diamond.

#### ABSTRACT

For many years, it was generally understood that a.c. transmission systems could not be controlled fast enough to handle dynamic system conditions. The dynamic system problems were usually handled by over-design, which resulted in under utilisation of the system. Flexible AC Transmission System (FACTS) devices play an important role in improving the dynamic performance of a power system and hence achieve better utilisation of the available system. They are principally employed to 'rapidly' control one or more of the three main parameters directly affecting a.c. power transmission, namely the system impedance, magnitude and phase angle of the system voltage. The Voltage Source Inverter (VSI) is the basic building block of most FACTS devices. The multi-level VSI topologies are becoming the favourite power circuits for the 2<sup>nd</sup> generation of FACTS shunt compensators.

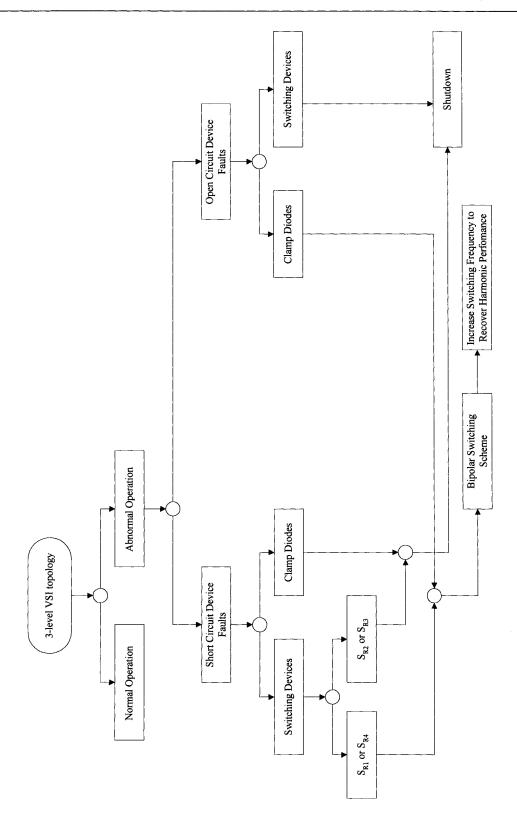

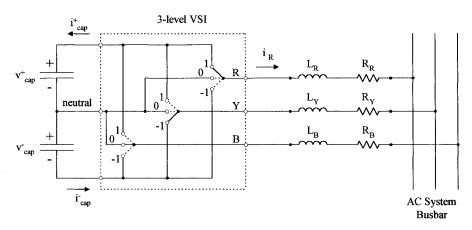

The research reported in this thesis is to investigate the reliability of Voltage Source Inverter topologies that are used in high power applications, mainly the Advanced Static VAr Compensator (ASVC). The inherent redundancy of the diode-clamped multi-level VSI topology, with respect to short-circuit and opencircuit device faults, is investigated using a space-vector nodal representation. The harmonic performance of the ASVC under normal and during 'device fault' operating conditions is also investigated.

A new multi-level inverter topology is proposed to improve the robustness of the conventional diode-clamped VSI topology. Harmonic spectrum 'recovery' techniques to be utilised in the event of device failure are also investigated and discussed. An adaptive PWM controller is proposed to maintain an acceptable low order harmonic performance for the ASVC under normal and abnormal operating conditions. The results obtained show that the proposed system can maintain uninterrupted operational performance throughout certain device failure conditions.

An experimental 3-level discharge path protection switch clamped (DPPSC) VSI system has been designed, constructed and analysed. To demonstrate the 3-level adaptive SHEM strategy, the adaptive DPPS controller was implemented on a TMS320F240 DSP evaluation module (EVM). The results were in good agreement with those predicted in the analytical and simulation parts of the work.

The research carried out in this work showed that under loaded operating conditions, the low frequency harmonic components targeted by SHEM techniques are not fully eliminated from the output voltage spectrum. This investigation revealed that this is due to the harmonic interaction between the a.c. and d.c. sides of the multi-level inverter. A new 'Dynamic Selective Harmonic Elimination Modulation (DSHEM)' scheme is proposed to overcome this problem. The DSHEM dynamically adjusts the switching angles according to the system operating point. The proposed method is verified using simulation and the experimental model.

### **CONTENTS**

#### PAGE

| ACKNOWLEDGEMENTS  | iv  |

|-------------------|-----|

| ABSTRACT          | v   |

| TABLE OF CONTENTS | vi  |

| NOMENACLATURE     | xii |

| CHAPTER | 1     | INTRODUCTION                                        | 1  |

|---------|-------|-----------------------------------------------------|----|

|         | 1.1   | The Electric Power System                           | 1  |

|         | 1.2   | Flexible AC Transmission Systems (FACTS)            | 2  |

|         | 1.3   | Scope of the Research Project                       | 3  |

|         | 1.4   | Overview of the Thesis                              | 4  |

| CHAPTER | 2     | REACTIVE POWER (VAR) COMPENSATORS                   | 6  |

|         | 2.1   | Introduction                                        | 6  |

|         | 2.2   | Shunt VAr Compensation                              | 6  |

|         | 2.3   | Conventional Shunt Compensators                     | 8  |

|         | 2.4   | 1 <sup>st</sup> Generation FACTS Shunt Compensators | 10 |

|         | 2.4.1 | Thyristor switched capacitor (TSC)                  | 11 |

|         | 2.4.2 | Thyristor controlled reactor (TCR)                  | 12 |

|         | 2.5   | 2 <sup>nd</sup> Generation FACTS Shunt Compensators | 16 |

|         | 2.5.1 | The current source inverter (CSI) based SVC         | 17 |

|         | 2.5.2 | The unrestricted frequency changer (UFC) based      |    |

|         |       | SVC                                                 | 17 |

|         | 2.5.3 | The voltage source inverter (VSI) based SVC         | 18 |

| CHAPTER | 3     | SHUNT STATIC VAR SYSTEM (SVS)                       | 25 |

|         |       | TOPOLOGIES                                          |    |

|         | 3.1   | Introduction                                        | 25 |

|         | 3.2   | Power Electronic Devices used in Shunt VAr          |    |

|         |       | Compensators                                        | 25 |

|         |       |                                                     |    |

|         | 3.3                                                                                                                                                  | Static VAr Compensator Topologies -                                                                                                                                                                                   |                                                          |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

|         |                                                                                                                                                      | 1 <sup>st</sup> Generation FACTS                                                                                                                                                                                      |                                                          |  |

|         | 3.3.1                                                                                                                                                | TCR topologies                                                                                                                                                                                                        | 29                                                       |  |

|         | 3.3.2                                                                                                                                                | Fixed capacitor, thyristor controlled reactor                                                                                                                                                                         |                                                          |  |

|         |                                                                                                                                                      | (FC/TCR)                                                                                                                                                                                                              | 30                                                       |  |

|         | 3.3.3                                                                                                                                                | Thyristor Controlled Reactor / Thyristor Switched                                                                                                                                                                     |                                                          |  |

|         |                                                                                                                                                      | Capacitor (TCR/TSC)                                                                                                                                                                                                   | 31                                                       |  |

|         | 3.4                                                                                                                                                  | ASVC Topologies – 2 <sup>nd</sup> Generation FACTS                                                                                                                                                                    | 33                                                       |  |

|         | 3.4.1                                                                                                                                                | Six-pulse voltage source inverter (VSI)                                                                                                                                                                               | 33                                                       |  |

|         | 3.4.2                                                                                                                                                | Multi-level VSI topologies                                                                                                                                                                                            | 36                                                       |  |

|         | 3.4.2.                                                                                                                                               | l Diode-clamped multi-level inverter (DCMLI)                                                                                                                                                                          | 37                                                       |  |

|         | 3.4.2.2                                                                                                                                              | 2 Flying capacitor converter (FCC)                                                                                                                                                                                    | 39                                                       |  |

|         | 3.4.2.3                                                                                                                                              | 3 Cascaded-inverter with separate DC sources                                                                                                                                                                          | 42                                                       |  |

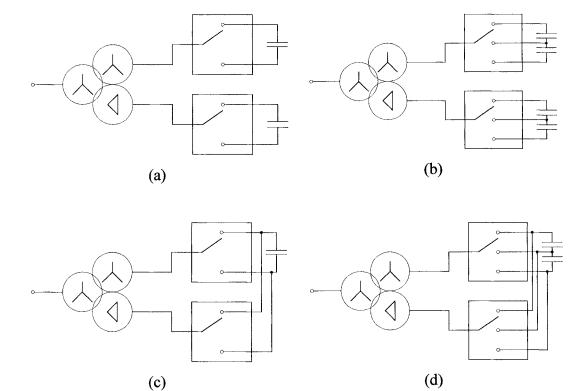

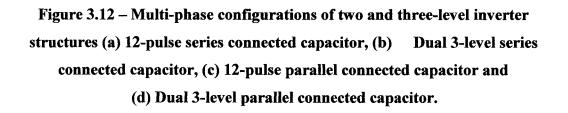

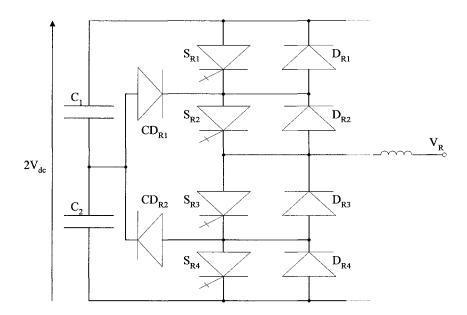

|         | 3.4.3                                                                                                                                                | Multi-phase / pulse VSI topologies                                                                                                                                                                                    | 44                                                       |  |

|         | 3.4.4                                                                                                                                                | Comparison of suitable VSI topologies                                                                                                                                                                                 | 46                                                       |  |

|         |                                                                                                                                                      |                                                                                                                                                                                                                       |                                                          |  |

|         |                                                                                                                                                      |                                                                                                                                                                                                                       |                                                          |  |

| CHAPTER | 4                                                                                                                                                    | DCMLI INHERENT REDUNDANCY                                                                                                                                                                                             | 48                                                       |  |

| CHAPTER | 4                                                                                                                                                    | DCMLI INHERENT REDUNDANCY<br>INVESTIGATIONS                                                                                                                                                                           | 48                                                       |  |

| CHAPTER | <b>4</b><br>4.1                                                                                                                                      |                                                                                                                                                                                                                       | <b>48</b><br>48                                          |  |

| CHAPTER |                                                                                                                                                      | INVESTIGATIONS                                                                                                                                                                                                        |                                                          |  |

| CHAPTER | 4.1                                                                                                                                                  | INVESTIGATIONS Introduction                                                                                                                                                                                           |                                                          |  |

| CHAPTER | 4.1                                                                                                                                                  | INVESTIGATIONS<br>Introduction<br>Representation of the 3-level VSI in Space Vector                                                                                                                                   | 48                                                       |  |

| CHAPTER | 4.1<br>4.2                                                                                                                                           | INVESTIGATIONS<br>Introduction<br>Representation of the 3-level VSI in Space Vector<br>Nodal Plane                                                                                                                    | 48<br>50                                                 |  |

| CHAPTER | 4.1<br>4.2<br>4.3                                                                                                                                    | INVESTIGATIONS<br>Introduction<br>Representation of the 3-level VSI in Space Vector<br>Nodal Plane<br>Robustness and Inherent Redundancy Investigation                                                                | 48<br>50<br>54                                           |  |

| CHAPTER | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                                                            | INVESTIGATIONS<br>Introduction<br>Representation of the 3-level VSI in Space Vector<br>Nodal Plane<br>Robustness and Inherent Redundancy Investigation<br>Two-Level VSI Investigations                                | 48<br>50<br>54<br>55                                     |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> </ul>                                                                        | INVESTIGATIONS<br>Introduction<br>Representation of the 3-level VSI in Space Vector<br>Nodal Plane<br>Robustness and Inherent Redundancy Investigation<br>Two-Level VSI Investigations<br>Short-circuit device faults | 48<br>50<br>54<br>55<br>56                               |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> </ul>                                                         | INVESTIGATIONS<br>Introduction                                                                                                                                                                                        | 48<br>50<br>54<br>55<br>56<br>59                         |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.5</li> </ul>                                            | INVESTIGATIONS<br>Introduction                                                                                                                                                                                        | 48<br>50<br>54<br>55<br>56<br>59<br>61                   |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.5</li> <li>4.5.1</li> </ul>                             | INVESTIGATIONS<br>Introduction                                                                                                                                                                                        | 48<br>50<br>54<br>55<br>56<br>59<br>61<br>62             |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.5</li> <li>4.5.1</li> <li>4.5.2</li> </ul>              | INVESTIGATIONS<br>Introduction                                                                                                                                                                                        | 48<br>50<br>54<br>55<br>56<br>59<br>61<br>62<br>69       |  |

| CHAPTER | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.5</li> <li>4.5.1</li> <li>4.5.2</li> <li>4.6</li> </ul> | INVESTIGATIONS<br>Introduction                                                                                                                                                                                        | 48<br>50<br>54<br>55<br>56<br>59<br>61<br>62<br>69<br>73 |  |

| CHAPTER | 5       | HARMONIC ANALYSIS & PERFORMANCE                   |            |

|---------|---------|---------------------------------------------------|------------|

|         |         | <b>RECOVERY DURING ABNORMAL</b>                   |            |

|         |         | OPERATING CONDITIONS                              | <b>9</b> 7 |

|         | 5.1     | Introduction                                      | 97         |

|         | 5.2     | Harmonic Analysis of the 3-Level VSI              | 97         |

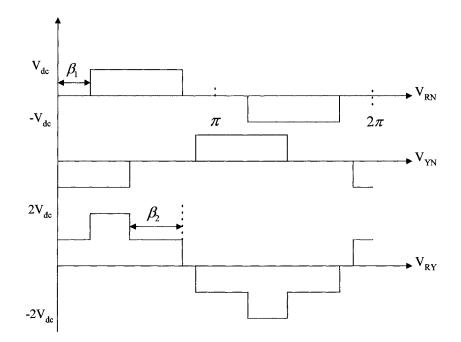

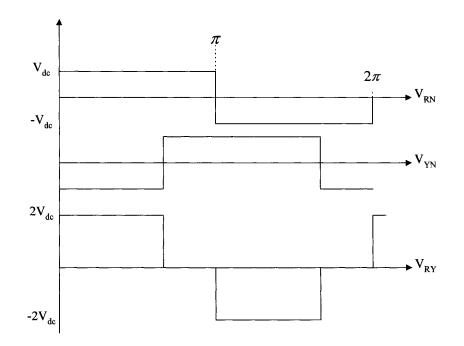

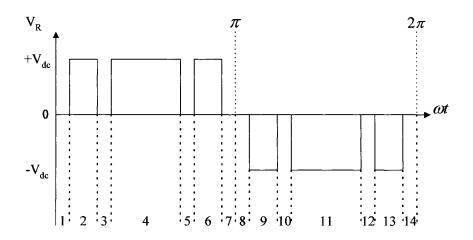

|         | 5.3     | Fundamental Frequency Modulation (FFM)            | <b>98</b>  |

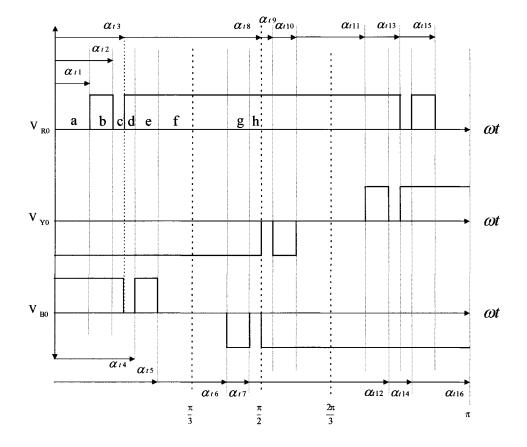

|         | 5.3.1   | Three-level VSI                                   | 98         |

|         | 5.3.2   | Two-level VSI                                     | 104        |

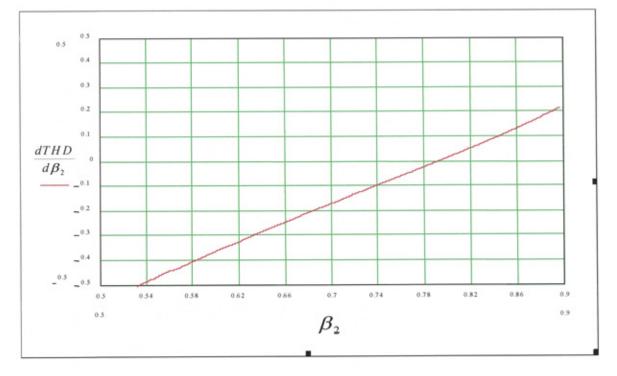

|         | 5.4     | Three-Level Selective Harmonic Elimination        |            |

|         |         | Modulation (SHEM)                                 | 107        |

|         | 5.4.1   | Recovery of 3-level SHEM harmonic performance     |            |

|         |         | under abnormal operating conditions               | 112        |

|         | 5.5     | Summary of Harmonic Analysis and Performance      |            |

|         |         | Recovery                                          | 116        |

|         |         |                                                   |            |

| CHAPTER | 6       | PROPOSAL OF A NEW ADAPTIVE                        |            |

|         |         | DISCHARGE PATH PROTECTION SWITCH                  |            |

|         |         | CLAMPED (DPPSC) MULTI-LEVEL VSI.                  | 119        |

|         | 6.1     | Introduction                                      | 119        |

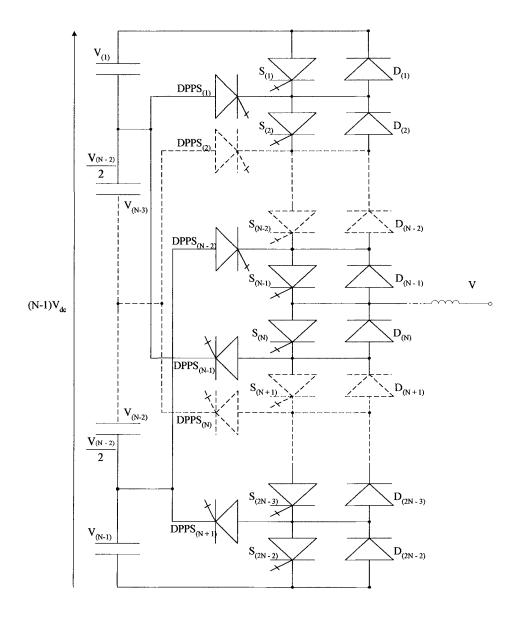

|         | 6.2     | The Adaptive 'N'-Level DPPSC-MLI Topology         | 119        |

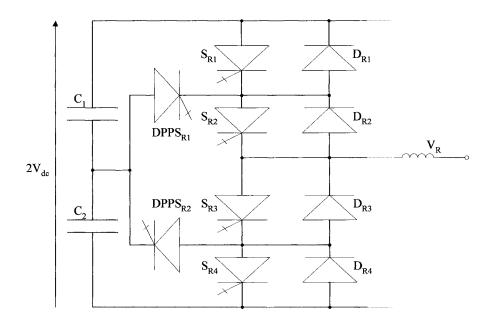

|         | 6.2.1   | The 3-level DPPSC-MLI topology                    | 122        |

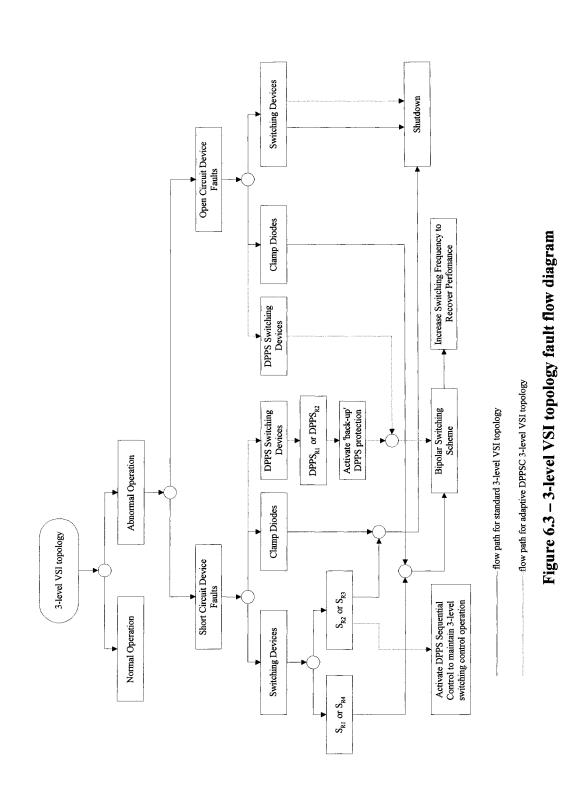

|         | 6.2.2   | The 3-level adaptive DPPS control strategy        | 125        |

|         | 6.2.2.1 | Normal operation control scheme                   | 126        |

|         | 6.2.2.2 | 2 Abnormal operation control scheme               | 128        |

|         | 6.3     | Structural Properties of the DPPSC-MLI Topology   | 133        |

|         | 6.4     | Effect of Adaptive Switching Control on Switching |            |

|         |         | Frequency                                         | 137        |

|         | 6.5     | Simulation of 3-Level DPPSC-MLI based ASVC        | 139        |

|         | 6.5.1   | The ASVC during normal operation                  | 140        |

|         | 6.5.2   | The ASVC during abnormal operation                | 145        |

|         | 6.5.3   | The ASVC during short-circuit device faults       | 149        |

| CHAPTER | 7       | CONSTRUCTION OF A LABORATORY                        |     |

|---------|---------|-----------------------------------------------------|-----|

|         |         | MODEL THREE-LEVEL DPPSC-MLI                         | 152 |

|         | 7.1     | Introduction                                        | 152 |

|         | 7.2     | Development of the Main Power Circuit               | 153 |

|         | 7.2.1   | The three-phase inverter circuit                    | 153 |

|         | 7.2.2   | IGBT Driver circuits                                | 156 |

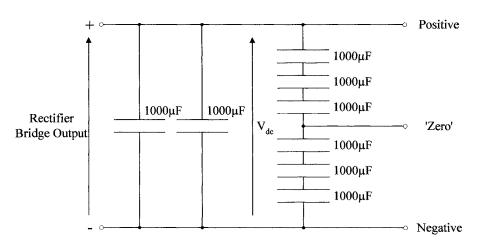

|         | 7.2.3   | The DC link and associated '3-Level' capacitor bank | 157 |

|         | 7.3     | Development of the DSP based Adaptive DPPS          |     |

|         |         | Controller                                          | 158 |

|         | 7.3.1   | Development of control hardware                     | 158 |

|         | 7.3.2   | Development of adaptive switching control software. | 161 |

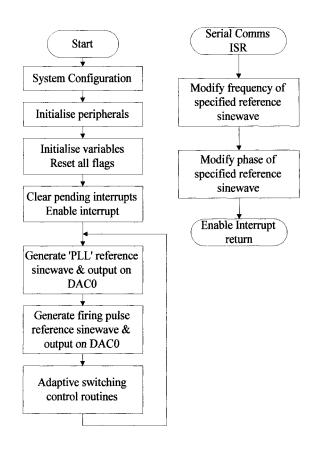

|         | 7.3.2.1 | Reference sinewaves and serial communication        | 161 |

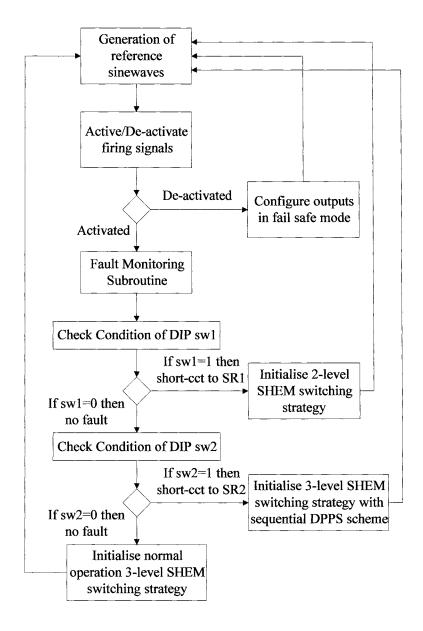

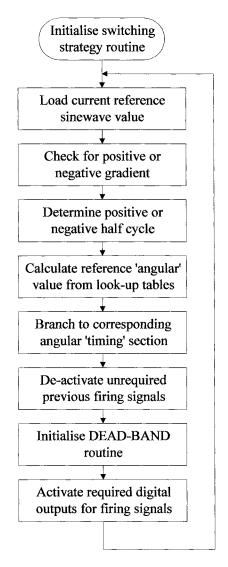

|         | 7.3.2.2 | Adaptive switching control algorithms               | 163 |

|         | 7.4     | Protection Circuits                                 | 170 |

|         | 7.4.1   | Hardware protection                                 | 170 |

|         | 7.4.2   | Software protection                                 | 171 |

|         | 7.5     | Construction of Complete Hardware Model             | 172 |

| CHAPTER | 8       | PERFORMANCE ANALYSIS OF 3-LEVEL                     |     |

|         |         | DPPSC-MLI                                           | 174 |

|         | 8.1     | Introduction                                        | 174 |

|         | 8.2     | Adaptive Topology Performance Under Normal &        |     |

|         |         | Abnormal Operating Conditions (Test 1)              | 174 |

|         | 8.2.1   | SHEM operated VSI system performance with no-       |     |

|         |         | load                                                | 177 |

|         | 8.2.2   | Three-level VSI performance with inductive load     |     |

|         |         | bank                                                | 187 |

|         | 8.2.3   | Harmonic performance of 3-Level VSI with            |     |

|         |         | inductive load                                      | 195 |

|         | 8.3     | Operating Performance of the 3-Level DPPSC-MLI      |     |

|         |         | based ASVC (Test 2)                                 | 201 |

|         | 8.4     | Summary of the Experimental Model Performance.      | 207 |

| CHAPTER | 9    | DYNAMIC SHEM (DSHEM) FOR A                        |     |

|---------|------|---------------------------------------------------|-----|

|         |      | 3-LEVEL VSI BASED ADVANCED                        | 210 |

|         |      | STATIC VAR COMPENSATOR                            |     |

|         | 9.1  | Introduction                                      | 210 |

|         | 9.2  | Switching Function Modelling of VSI based ASVC    |     |

|         |      | Operation                                         | 211 |

|         | 9.3  | 3-Level Modulation Analysis and Proposal of       |     |

|         |      | DSHEM                                             | 215 |

|         | 9.4  | ASVC Simulations with Conventional SHEM &         |     |

|         |      | Dynamic SHEM                                      | 222 |

|         | 9.5  | Experimental Verification of 3-Level DSHEM        | 227 |

|         | 9.6  | Discussions of DSHEM Performance                  | 231 |

| CHAPTER | 10   | CONCLUSIONS                                       | 232 |

|         | 10.1 | Robustness and Inherent Redundancy Investigations |     |

|         |      | for the Diode-Clamped Multi-level VSI             | 233 |

|         | 10.2 | The Adaptive DPPSC-MLI Topology                   | 233 |

|         | 10.3 | Development of ASVC Laboratory Model              | 234 |

|         | 10.4 | Performance Analysis of the Proposed System       | 235 |

|         | 10.5 | The Dynamic SHEM Scheme                           | 236 |

|         | 10.6 | Suggestions for Further Research                  | 236 |

#### REFERENCES

#### 238

####

#### **APPENDIX B**

# 4-LEVEL AND 5-LEVEL VSI TOPOLOGY REDUNDANCYINVESTIGATION250

268

| APPENDIX C                                 |     |

|--------------------------------------------|-----|

| FOURIER ANALYSIS FOR VSI VOLTAGE WAVEFORMS | 256 |

#### **APPENDIX D**

| EXPERIMENTAL MODEL DESIGN AND CONSTRUCTION              | 264 |

|---------------------------------------------------------|-----|

| D.1 Design of Single IGBT Driver Circuit                | 264 |

| D.2 IGBT and Driver Circuit Testing                     | 265 |

| D.3 The DC Link and Associated '3-level' Capacitor Bank | 266 |

#### **APPENDIX E**

# IMPLEMENTING THE ADAPTIVE DPPS CONTROL ON THE TMS320F240 DSP

| E.1 Generating the Reference Sinewave                           | 268 |

|-----------------------------------------------------------------|-----|

| E.1.1 Section of assembly language code for generating sinewave | 269 |

| E.2 Developing the Adaptive DPPS code for a 3-level SHEM to 2-  |     |

| Level SHEM Switching Strategy                                   | 271 |

| E.2.1 Initialisation of switching strategy gradients            | 271 |

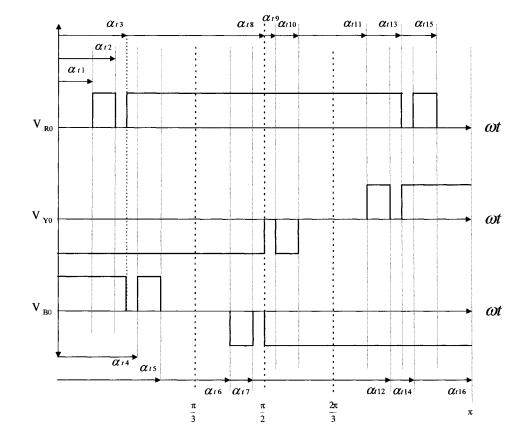

| E.2.2 Implementation of the adaptive 3-level SHEM strategy      | 272 |

| E.2.3 Implementation of the 2-level SHEM strategy               | 274 |

|                                                                 |     |

#### **APPENDIX F**

| THREE-LEVEL         | VSI | (SHEM) | SWITCHING | FUNCTION | AND |     |

|---------------------|-----|--------|-----------|----------|-----|-----|

| <b>MODULATION</b> A | NAL | YSIS   |           |          |     | 275 |

#### NOMENCLATURE

| α                | SHEM firing angle                                             |

|------------------|---------------------------------------------------------------|

| β                | Modulation angle                                              |

| a.c.             | Alternating current                                           |

| ADC              | Analogue to digital converter                                 |

| ASVC             | Advanced static VAr compensator                               |

| В                | Blue                                                          |

| С                | Capacitor                                                     |

| CD <sub>XY</sub> | Clamp diode (x indicates phase, y indicates limb position)    |

| CSI              | Current source inverter                                       |

| d.c.             | Direct current                                                |

| DAC              | Digital to Analogue converter                                 |

| DCMLI            | Diode-clamped multi-level inverter                            |

| DPPS             | Discharge path protection switch                              |

| DSHEM            | Dynamic selective harmonic elimination modulation             |

| DSP              | Digital signal processor                                      |

| DSSPC-MLI        | Discharge path protection switch clamped multi-level inverter |

| FACTS            | Flexible AC transmission systems                              |

| FC               | Fixed capacitor                                               |

| FFM              | Fundamental frequency modulation                              |

| GTO              | Gate turn-off thyristor                                       |

| HVDC             | High voltage direct current                                   |

| I                | AC current                                                    |

| I/O              | Input / output                                                |

| i <sub>cap</sub> | Capacitor current                                             |

| IGBT             | Insulated gate bi-polar transistor                            |

| L                | Inductor                                                      |

| MSC              | Mechanically switched capacitor                               |

| MSR              | Mechanically Switched reactor                                 |

| NPC              | Neutral point clamped                                         |

|                  |                                                               |

| PLL               | Phase locked loop                                     |

|-------------------|-------------------------------------------------------|

| PWM               | Pulse width modulation                                |

| R                 | Red                                                   |

| R                 | Resistor                                              |

| rms               | Root mean square                                      |

| SHEM              | Selective harmonic elimination modulation             |

| SVC               | Static VAr compensator                                |

| S <sub>XY</sub>   | Switch (x indicates phase, y indicates limb position) |

| TCR               | Thyristor controlled reactor                          |

| THD               | Total harmonic distortion                             |

| TSC               | Thyristor switched capacitor                          |

| UFC               | Unrestricted frequency changer                        |

| V                 | AC voltage                                            |

| VAr               | Volt-amperes reactive (reactive power)                |

| V <sub>ASVC</sub> | ASVC output voltage                                   |

| V <sub>cap</sub>  | Capacitor voltage                                     |

| V <sub>CE</sub>   | Collector-emitter voltage                             |

| V <sub>dc</sub>   | DC voltage across each capacitor unit                 |

| Vs                | AC system voltage                                     |

| VSI               | Voltage source inverter                               |

| X                 | Inductive reactance                                   |

| Y                 | Yellow                                                |

## **1 INTRODUCTION**

#### 1.1 THE ELECTRIC POWER SYSTEM

The continual research and analysis over the last few decades has led to a worldwide acknowledgement throughout electric power engineering that the a.c. electric power system, at transmission and distribution levels, requires parameter control as an integral design factor to ensure a reliable and secure provision of electrical energy to the consumer.

The concept of network control through implementation of reactive power (VAr) compensators, to increase the transmittable power in an a.c. power system, is a well-established technique [1]. At the beginning of the 20<sup>th</sup> century, basic fixed quantity VAr compensators were implemented to improve the steady-state characteristics of the power system. The necessity for a dynamic controllable reactive power compensation system was recognised in 1931 with Friedlander's shunt connected saturated reactor [2]. These early controllers were implemented essentially to improve the overall transmission capabilities that were being restricted due to the reactance associated with a long transmission line and to compensate for predetermined loads throughout the system.

More recently, since the Electricity Act of 1989, the deregulation of the UK electric supply industry has had a profound effect upon the need for the optimum utilisation of the currently available transmission and distribution networks. The electrical utilities and power industry throughout the world are experiencing radical changes due to a generalizing world economy and trend towards liberalisation. This progress will effect not only the traditional electrical power generation but also the transmission and distribution of energy [3]. Whilst the last few decades has shown a growing worldwide demand for electrical energy, the new generation of environmentalists have canvassed for the restriction of the construction of new transmission lines with the knowledge of under-utilisation of existing networks.

Coupled with the economic restrictions is the resultant competitive market factor of the deregulation and privatisation of the electrical power industry. Throughout the world, utilities are recruiting customers that may, in some cases, be located thousands of miles from the utilities regular operational location. In the UK this has filtered through in the last few years to the domestic customer with various energy suppliers offering a cheap yet reliable provision of power irrespective of the consumers location. This epitomises the criticality of a reliable interconnection of transmission and distribution systems and the radical improvements required in the dynamics and methodologies of a.c. system control.

#### 1.2 FLEXIBLE AC TRANSMISSION SYSTEMS (FACTS)

The necessity of improved control techniques to meet the worldwide increasing demands for more power, higher quality and improved reliability has led to the development of power electronic configurations of the conventional reactive power (VAr) controllers. In the late 1980's the Electric Power Research Institute (EPRI) commissioned a new technology referred to as Flexible AC Transmission Systems (FACTS). The term FACTS is defined by the IEEE PES Task Force of the FACTS Working Group as [4]:

Flexible AC Transmission System (FACTS). Alternating current transmission systems incorporating power electronic- based and other static controllers to enhance controllability and increase power transfer capability.

The technology was intended to offer solutions for transient stability control and hence improve utilisation of transmission networks. The FACTS controllers immediately arrived in two generations. The currently implemented a.c. system controllers using thyristors were grouped as 1<sup>st</sup> generation. Whilst proposals of improved solid-state inverter based topologies were classified as the 2<sup>nd</sup> generation of FACTS. A wide range of power electronic-based FACTS controllers are becoming routinely employed in order to enhance the power transfer capabilities of the otherwise under-utilised parts of an interconnected network.

One of the first representatives of the large 2<sup>nd</sup> generation FACTS controllers to be constructed was known as the Advanced Static VAr Compensator (ASVC). Proposed by Gyugyi [5], the shunt reactive power compensation topology offers a dynamically responsive improvement to the conventionally implemented synchronous condenser. The voltage source inverter (VSI) is thought off as the building block of the ASVC and many other FACTS controllers. With the series and shunt control techniques being established, the development of various multilevel inverter topologies has become the focus of many research establishments. The sections of the network that FACTS devices are applied to are typically integral in terms of maintaining system stability and optimal power flows. Therefore, it is crucial that the VSI topology implemented within the FACTS controller offers a reliable and optimum level of performance.

#### 1.3 SCOPE OF THE RESEARCH PROJECT

The research presented in this thesis studied the steady-state (open-loop) performance of the diode clamped multi-level voltage-source-inverter topology applied to the Advanced Static VAr Compensator. Initially, an overview of shunt VAr compensation and possible topologies for VAr compensators are presented. An investigation of the inherent redundancy and overall robustness of the diode clamped multi-level inverter (DCMLI) in the event of a power circuit device fault is described. Low frequency switching scheme harmonic analysis is presented to illustrate how the limitations of the investigated topology can be overcome. A 'new' adaptive DCMLI topology and control scheme is proposed.

To verify the validity of the new system, a 3-phase multi-level adaptive DCMLI, implemented with a TMS320F240 digital signal processor (DSP), was developed. Comparative analysis between theoretical predictions and practical results is observed. Finally, the harmonic and overall performance of the DCMLI based ASVC under VAr compensation conditions are investigated. The effect of the 'idealised' PWM schemes on the overall performance of the DCMLI is investigated and a Dynamic Selective Harmonic Elimination Modulation (DSHEM) scheme is proposed. The improved performance is verified through practical implementation.

#### **1.4 OVERVIEW OF THE THESIS**

**Chapter 2:** A summarized historical background of power system reactive power (VAr) compensators, specifically shunt, to assist in the steady-state and dynamic stability of a transmission system is presented. Conventional compensators and new concepts used in FACTS technologies are introduced. An overview of the principles of the Advanced Static VAr Compensator (ASVC) is also presented.

**Chapter 3:** The topologies of  $1^{st}$  generation – variable reactive admittance – Static VAr Compensator (SVC) and  $2^{nd}$  generation – solid-state converter – Advanced Static VAr Compensator (ASVC) are presented. Voltage source inverter (VSI) topologies suitable for high power ASVC application such as the conventional six-pulse VSI, the multi-level VSI topologies and the multi-phase configurations are discussed.

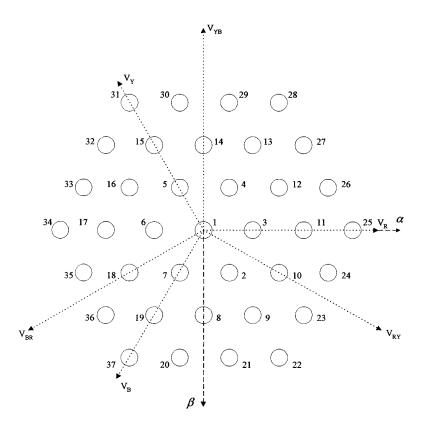

**Chapter 4:** The inherent redundancy of the stand-alone diode-clamped multilevel voltage-source-inverter (DCMLI) is investigated. Representation of the 3level DCMLI topology in the space vector nodal plane is derived. Short-circuit and open-circuit device fault investigations are demonstrated. The Chapter is concluded with an observation of the robustness and the possibility of redundancy in the event of a device fault.

**Chapter 5:** Harmonic analysis of the stand-alone VSI structures suitable for the ASVC applications is presented. Firstly, optimised strategies for fundamental frequency modulation (FFM) are presented. Secondly, the selective harmonic elimination modulation (SHEM) harmonic recovery strategies are presented and discussed.

**Chapter 6:** This Chapter describes a new topology proposed to increase the robustness of the DCMLI system. The DCMLI topology implementing an adaptive discharge-path protection switch is presented. Operational considerations together with a new adaptive control scheme are discussed. Simulation results of

the adaptive 3-level VSI ASVC topology are given to illustrate the operation under normal and abnormal conditions.

**Chapter 7:** The construction of the laboratory model adaptive multi-level VSI employing a DSP controller is explained in this Chapter. Development of the power circuit and associated drivers together with the adaptive controller is presented. Fault sensing requirements and programming of the TMS320F240 DSP are also described.

**Chapter 8:** In this Chapter, the performance of the experimental laboratory model adaptive 3-level VSI based ASVC is analysed. The results of the three-phase 3-2 level VSI operation are discussed. Reactive power flow is demonstrated using a generalised machine and open-loop control.

**Chapter 9:** This Chapter investigates the harmonic interaction between the a.c. and d.c. sides of a 3-level inverter used as an Advanced Static VAr Compensator (ASVC). It is illustrated that due to the 3<sup>rd</sup> harmonic voltage across each d.c. side capacitor, the conventional SHEM scheme may not actually eliminate the target harmonics when the system is on load. A new modulation method, which dynamically adjusts the switching angles according to the operating point, is proposed to overcome this difficulty. The proposed method is verified using experimental and simulation results.

**Chapter 10:** This Chapter summarises and discusses the conclusions drawn from the theoretical analysis, simulations and the laboratory work of the entire project. Suggestions are given for further work.

### 2 REACTIVE POWER (VAR) COMPENSATORS

#### 2.1 INTRODUCTION

The overall operation of the a.c. transmission system is governed by the following interrelated parameters: series impedance, current, voltage and phase angle [4]. These parameters can be controlled, corresponding to the utility demand, by conventional controllers and recently by rapid-response power electronics in the form of FACTS controllers. The available controllers can generally be categorised into series, shunt and combined (series-shunt) controllers which can be applied individually or in coordination with each other to provide control of one or more of the system parameters. Although there is a necessity for all types of system controller, strategically positioned throughout a power system network, this project concentrates on the shunt VAr compensator only.

This Chapter presents the importance of shunt VAr compensation together with a review of the conventional and state of the art FACTS controllers available for such an application. The final section presents a detailed description of the principles of the Advanced Static VAr Compensator (ASVC), the FACTS controller to which this project is focussed upon.

#### 2.2 SHUNT VAR COMPENSATION

If a power system is separated into its basic elements it can generally be categorised into three main components: generation, transmission or distribution and loads. This project investigates the concept of reactive power compensation, where the main objective is to strengthen the transmission and distribution systems. The most basic representation of the transmission line is with reactive ladder networks composed of series inductors and shunt capacitors [4,6]. From inductor (L) and capacitor (C) component first principles it is apparent that the series inductance determines the maximum transmittable power, whereas the shunt capacitance influences the voltage profile and thereby the power

transmission along the line. The problem of reactive power control therefore runs hand in hand with the voltage control problem, as a reactive power imbalance results in an inherent voltage deviation in the transmission line. This is further discussed in Appendix A.

Reactive power (VAr) control in the form of shunt compensation is a scheme that provides voltage support and assists in improving the overall performance of the a.c. power system. Shunt VAr compensation may be applied at a number of points such as intermediate switching stations or at load tee-off points along the transmission line [2]. The optimum positioning of the shunt VAr compensator is dependent upon the infrastructure of the transmission line. If a line is interconnecting two a.c. system buses then midpoint compensation is the most effective for voltage support. Whereas for a radial line, which is typical in a decentralised form of generation such as wind turbines, it is evident that the end of the line is the best location for the compensator. This is because the largest voltage variation is experienced at the end of the line that may, under extreme transient conditions, suffer from voltage collapse. The implementation of reliable and fast VAr compensators is becoming ever more critical with the increasing complexities of the modern a.c. power system.

#### 2.3 CONVENTIONAL SHUNT COMPENSATORS

The requirement of VAr controllers has long been recognised. The simplest and cheapest form of shunt VAr compensation is the fixed capacitor (FC) and its counterpart the fixed shunt reactor, shown in Figure 2.1(a). This type of compensation has been used for a.c. power transmission since the beginning of the last century. It is the 'belt and braces' technique and simply acts upon the steady-state transmission characteristics. Fixed capacitors are used to compensate for known large inductive load points and to provide voltage support throughout the transmission network, hence maintaining the required voltage profile. Whereas, fixed shunt reactors are used to limit the transient and temporary overvoltages due to load rejection, faults or line energisation. Unfortunately this fixed form of compensation reduces the power transfer capacity and surge impedance power by about 20% [6].

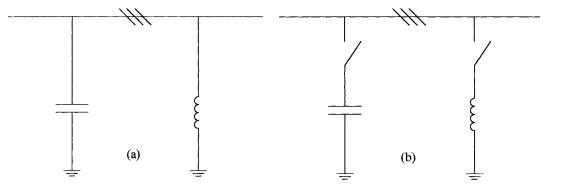

# Figure 2.1 – (a) Fixed Capacitor and Reactor, (b) Mechanically Switched Capacitor (MSC) and Mechanically Switched Reactor (MSR)

Resulting from this risk of system instability these basic fixed system controllers were complemented by controlled reactive compensation in the form of mechanically switched capacitors (MSC) and reactors (MSR), illustrated in Figure 2.1(b). The MSC and MSR enable provision of additional VAr generation or absorption in the event of large variation in system loading or voltage levels. Modern power capacitors have a high unit-capacity, small losses, good reliability and long time of operation and it is not uncommon to find them implemented into a hybrid scheme with more advanced FACTS technology [4,7].

The severe limitation of these compensators is that they could only compensate for steady-state slow variations and offered no continuously variable compensation. The necessity of compensation controllers offering a dynamic response with continuously variable generation or absorption of reactive power was traditionally satisfied with the implementation of rotating synchronous machines or synchronous condensers. By controlling the excitation of a mechanically unloaded synchronous machine, shown in Figure 2.2, the a.c. power system could be supplied with a controllable quantity of capacitive or inductive reactive power. At times of high inductive loading on the power system the compensator runs over-excited and generates reactive power. At times of light loads the machine is under-excited to absorb reactive power. Later, the dynamic stability and therefore the security and reliability of the a.c. power system was further assisted by the implementation of saturated reactors in conjunction with fixed capacitors [4].

Figure 2.2 - Synchronous Condenser

9

The critical downfall of these conventional techniques is that they simply cannot provide the accuracy, of the controllable power flow, that is essential due to the complexities of today's power networks. Also, due to the speed of response being restricted to the mechanical switching time, in the case of the MSC and MSR, or the slow response of the synchronous machine the conventional controller cannot realize the dynamic response requirements necessary to maintain an operable secure system functional at close to its maximum transmittable power. While the saturated reactor compensator has a faster response it is bulky, expensive and its control is not flexible. It is well known that in the past this resulted in the under utilisation of the transmission system and very generous stability limits. This resulted in the system being operated far below its thermal rated capacity. Another major drawback of these system controllers is the maintenance required and the relatively short lifespan when compared to the more modern topologies.

### 2.4 1<sup>st</sup> Generation FACTS Shunt Compensators

Advances in high-power thyristor technology, increasing demands for improvements of the performance of transmission systems and the need for compensation of large industrial loads (such as electric arc furnaces), prompted the development of improved continuously variable VAr compensators. The first development was simply to replace the mechanically switched control with thyristor power switches, and precision controllers, to improve the response time and accuracy. By the late 1960's several large installations of shunt VAr compensators had started to appear using these new controllable static VAr sources [5].

The 1<sup>st</sup> generation of shunt FACTS static VAr generators (SVG's) maintained the variable reactive admittance technique of the traditional controller by still utilising the passive (L and C) components to vary the transmission line system parameters, but improved control precision with the use of thyristors. The term SVG is defined by the IEEE PES Task Force of the FACTS Working Group as [4]:

Static VAr Generator or Absorber (SVG): A static electric device, equipment, or system that is capable of drawing controlled capacitive and/or inductive current from an electric power system and thereby generating or absorbing reactive power. Generally considered to consist of shunt-controlled, thyristor-controlled reactor(s) and/or thyristor-switched capacitors.

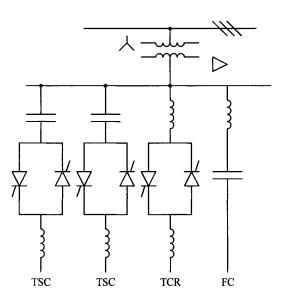

#### 2.4.1 THYRISTOR SWITCHED CAPACITOR (TSC)

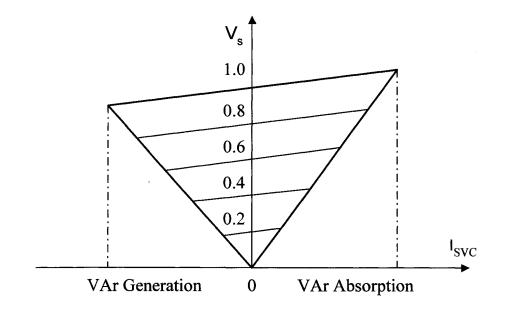

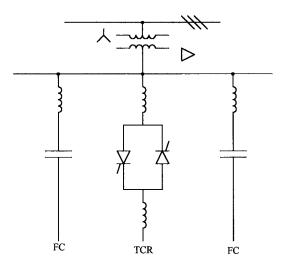

The thyristor switched capacitor (TSC) VAr compensator utilises a capacitor in series with a bi-directional thyristor pair and a small reactor, as shown in Figure 2.3. The operation of the TSC is quite simple with the thyristors switching in a fixed quantity of shunt capacitive admittance if reactive power compensation is required. The purpose of the reactor is to limit switching transients, to damp inrush currents and to form a filter for harmonics coming from the power system or from any parallel-connected reactive power compensator. For 3-phase systems the delta connection of the 3-phase TSC is preferred as the 3<sup>rd</sup> harmonic is cancelled out under symmetrical conditions. The delta connection of the TSC is shown in Figure 2.4.

Figure 2.3 – Thyristor Switched Capacitor (TSC)

By connection of several TSC branches in parallel, it is possible to make the compensation as accurate as desired. A technique that is utilised is the binary system in which the total number of capacitors is divided into groups with each group taking the subsequent binary value, i.e. 1, 2, 4, 8, 16, etc. The smallest capacity is chosen in order for the required precision. This binary system gives a greater flexibility of compensation [8]. The TSC suffers mainly from high cost and the complexity of controls.

Figure 2.4 – Delta connected 3-phase Thyristor Switched Capacitor (TSC)

#### 2.4.2 THYRISTOR CONTROLLED REACTOR (TCR)

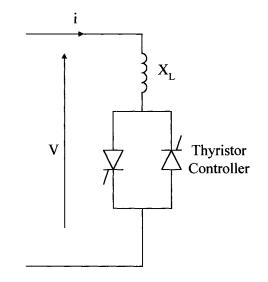

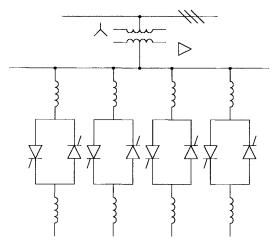

The basic thyristor controlled reactor (TCR), shown in Figure 2.5, consists of a reactor in series with a bi-directional thyristor pair. The compensator operates by the thyristors conducting on alternate half cycles of the supply frequency.

Adjusting the conduction interval of the inverse parallel-connected thyristors controls the current flow in the inductor (L). This is achieved by delaying the turn-on of the thyristor switch by a firing angle ( $\alpha$ ) in each half cycle with respect to the voltage zero. If  $\alpha = 90^{\circ}$  the current is essentially reactive and sinusoidal [9]. Conduction is obtained with firing angles between 90° and 180°. Conduction angles of the two thyristors must be kept equal, as unequal conduction angles will produce even harmonic components in the current, including a d.c. value.

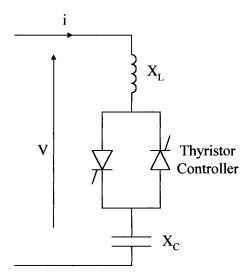

Figure 2.5 – Thyristor Controlled Reactor (TCR)

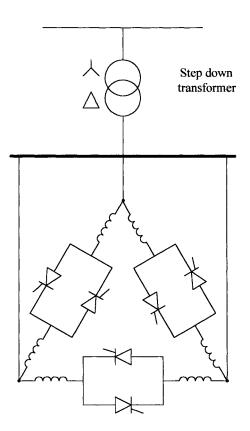

Even with symmetrical positive and negative half cycles of current the phase control operation of the TCR results in the generation of unwanted odd harmonics (in addition to the required fundamental current). This is due to the non-sinusiodal current waveform in the reactor. TCR configurations to improve the harmonic quality of the output current are presented in Chapter 3. For 3-phase applications the TCR can be connected in star or delta. As with the TSC the delta connection, shown in Figure 2.6, is preferred for the 3-phase TCR. This is due to the improved harmonic performance as under balanced conditions the triplen harmonics (3<sup>rd</sup>, 9<sup>th</sup>, 15<sup>th</sup>, etc.) circulate in the delta and therefore do not enter the power system.

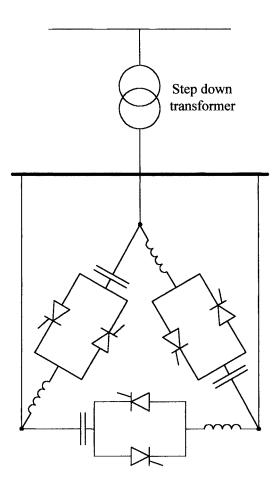

Figure 2.6 – Delta connected 3-phase Thyristor Controlled Reactor (TCR)

The thyristor controlled reactor (TCR) or thyristor switched capacitor (TSC) found much commercial success. This was due to their 'acceptable' cost, response time, control flexibility, very little maintenance and relatively simple thyristor switch arrangements [5]. It should be noted however that although these SVG's could be used individually, they were more effectively implemented combined (TSC-TCR) as a hybrid static VAr Compensator (SVC). The term SVC is defined by the IEEE PES Task Force of the FACTS Working Group as [4]:

Static VAr Compensator (SVC): A shunt-connected static VAr generator or absorber whose output is adjusted to exchange capacitive or inductive current so as to maintain or control specific parameters of the electrical power system.

The Static VAr Compensator (SVC) is one of the most commonly used compensation techniques in power systems [10]. There are many hybrid arrangements reported and various topologies to improve the operational characteristics of these systems, as will be further described in Chapter 3. The SVC schemes consisting of either thyristor switched capacitors (TSC), thyristor controlled reactors (TCR), or both, provided a means of improved dynamic VAr compensation. However, as the SVC utilises passive components, the capacitor or inductor needs to be fully rated to generate or absorb the required reactive power. Also, a thyristor switching circuit rated at the sum of the maximum capacitive and inductive output is also required to control it. Therefore, SVC's are large systems that involve a number of major components, requiring a considerable size facility, particularly for the passive components.

When the first SVC's were developed, the solid-state power electronics represented the major share of the total equipment cost. By the 1980's the power handling capability of the power electronic devices had increased and devices such as high power Gate Turn Off (GTO) thyristors had started to emerge. This resulted in a drastic reduction in the total cost of switching devices required for a high power SVC [11]. Even with the advances in solid-state technology the effects on the total cost and size of the SVC was negligible, due to the large cost of the passive elements. Therefore a move towards an entirely solid-state compensation system was inevitable in order to achieve improvements in size, cost, control and dynamic performance.

#### 2.5 2<sup>ND</sup> GENERATION FACTS SHUNT COMPENSATORS

The new solid-state inverter based compensator, proposed by Gyugyi in 1979 [5], defined the  $2^{nd}$  generation of FACTS shunt compensator. The principle is to replace the large passive elements that are used for generation or absorption of reactive current with force-commutated power electronic inverter topologies resulting in fully solid-state compensators.

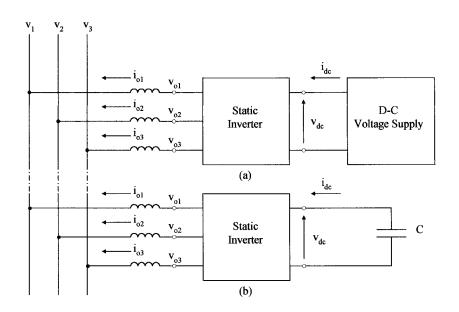

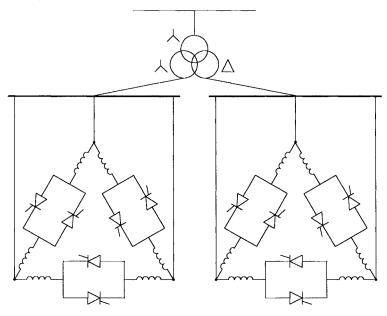

In the 2<sup>nd</sup> generation of FACTS shunt compensators, which was essentially the 3<sup>rd</sup> generation of shunt compensators, the generation of reactive power is obtained by switching devices with minimum passive elements. Static solid-state reactive power (VAr) compensators were proposed based on three topologies, current source inverter (CSI), unrestricted frequency converter (UFC) and voltage source inverter (VSI) as illustrated in Figures 2.7-2.9, respectively. Gyugyi's principle encapsulated both leading and lagging current to voltage phase quadrature requirements for an entire SVC in one unit. These systems are known as static synchronous compensators (STATCOM) and in Europe are more commonly referred to as Advanced Static VAr Compensators (ASVC). The term STATCOM or ASVC is defined by the IEEE PES Task Force of the FACTS Working Group as [4]:

*Static Synchronous Compensator (STATCOM):* A static synchronous generator operated as a shunt-connected static VAr compensator whose capacitive or inductive output current can be controlled independent of the a.c. system voltage.

This definition assumes that the compensator is used to provide reactive support at an infinite busbar. Throughout this project the compensator will be referred to as an ASVC unless reference literature (IEEE) is quoted. The characteristics and operation of the three topologies of solid-state VAr compensators proposed by Gyugyi [5] are summarised in this section. A more detailed description of the voltage source inverter (VSI) based shunt compensator, currently considered the most practical compensator for high power applications, is given in the subsequent section.

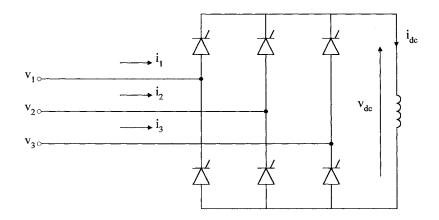

#### 2.5.1 THE CURRENT SOURCE INVERTER (CSI) BASED SVC

By utilising an inductively loaded a.c./d.c. six-pulse converter, shown in Figure 2.7, a current source type VAr generator can be realised. The converter may be line-commutated or force-commutated utilising conventional thyristors or devices with a turn off capability. The naturally (line) commutated converter can only provide lagging (absorb) reactive power compensation. To enable leading (generating) reactive current the converter must have its inputs shunted by three appropriately rated capacitor banks such that the combined current drawn from the a.c. system becomes leading as the converter current is decreased [5]. The force-commutated configuration will have anti-parallel diodes with its power switching devices and therefore will provide both lagging and leading VArs.

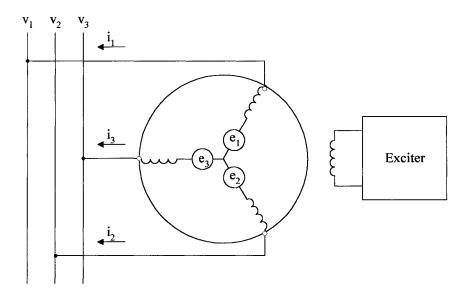

Figure 2.7 – Current Source Inverter (CSI) power circuit

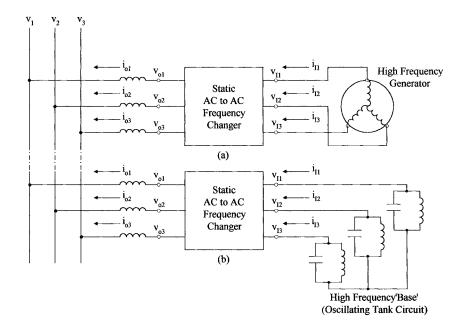

#### 2.5.2 THE UNRESTRICTED FREQUENCY CHANGER (UFC) BASED SVC

The unrestricted frequency changer based SVC is an alternative method of the operating principles of the rotating synchronous condenser, shown in Figure 2.2. The UFC SVC topology, as illustrated in Figure 2.8, can be implemented in two forms. Either utilising a high frequency generator or a multi-phase static oscillating LC tank circuit with a static a.c./a.c. frequency converter such as a force commutated cycloconverter. Considering Figure 2.8(a), a generator of relatively high frequency feeds a static a.c./a.c. frequency changer that converts

the generator frequency to the a.c. system frequency. By controlling the converter output voltages, in phase with the a.c. system voltages, by simple amplitude control the reactive power can be supplied in either direction to the a.c. system. Since the high frequency generator theoretically handles only reactive power it can be replaced with a multi-phase static oscillating LC tank circuit, as shown in Figure 2.8(b) [5].

# Figure 2.8 – Voltage Source SVC using a.c. to a.c. frequency changer. (a) Conventional high frequency a.c. source arrangement. (b) Self-sufficient LC tank circuits (HF base) operation.

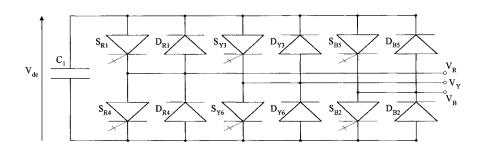

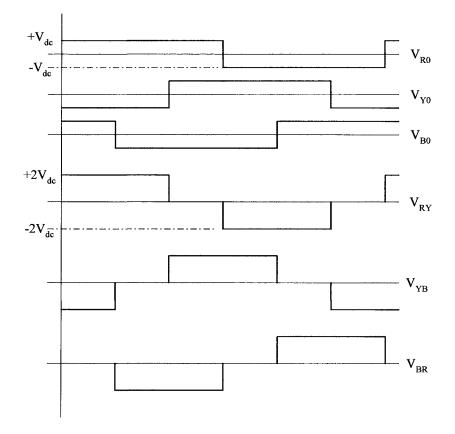

#### 2.5.3 THE VOLTAGE SOURCE INVERTER (VSI) BASED SVC

The voltage source inverter based SVC, shown in Figure 2.9, is essentially a static realisation of the conventional rotating synchronous condenser shown in Figure 2.2. The 'exciter' or d.c. voltage source shown in Figure 2.9 can be one of two forms, a d.c. voltage supply or storage capacitor, as illustrated in Figure 2.9.

Figure 2.9 – Voltage Source SVC using a d.c./a.c. inverter. (a) Conventional d.c. supply arrangement. (b) Self-sufficient storage capacitor operation.

By controlling the 3-phase inverter output voltages to be in phase with the a.c. system voltage the direction and magnitude of reactive current can be controlled through amplitude control of the output voltages. As with the excitation principles of the synchronous condenser, increasing the amplitude of the inverter output voltages ( $V_{o1} - V_{o3}$ ) above the a.c. system voltages ( $V_1 - V_3$ ) causes the generation of reactive power, whereas decreasing the inverter output voltage below the a.c. system voltage causes absorption of reactive power. It should be noted that due to the losses associated with the system a small amount of real power is made to flow from the a.c. system under both leading and lagging compensation modes.

The first reported solid-state static VAr compensator using force-commutated thyristors was reported for a 20 MVAr installation by Sumi in the early 1980s [12]. Edwards then demonstrated the feasibility of the new generation of reactive power compensators using GTO's in a  $\pm 1$  MVAr experimental installation [13]. Then, in 1993 Mori reported an  $\pm 80$  MVAr installation in Japan [14]. Since the initial proposal of the solid-state VAr compensator both CSI and VSI inverter

topologies have been investigated for suitability as a stand-alone compensator [15,16,17,18]. The development of the practical installations and research has shown the VSI topology to be most suitable, and therefore favoured, for the application due to comparatively low losses and overall improved performance.

#### **OPERATING PRINCIPLES OF THE VSI BASED ASVC**

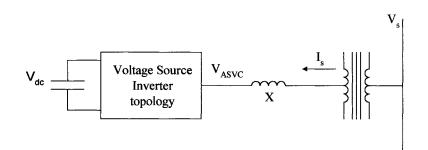

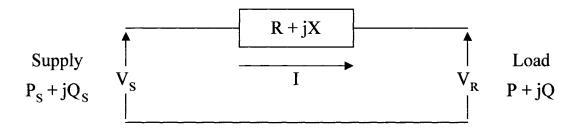

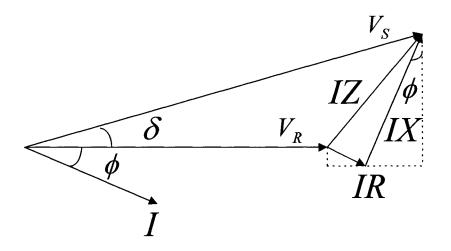

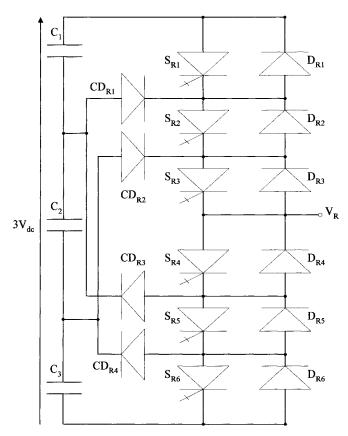

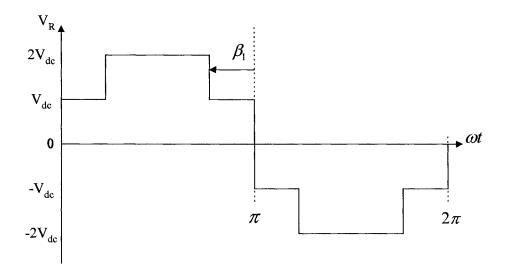

Many publications have demonstrated the operating principles and overall control of the VSI based ASVC. The general operating principles are described here assuming a 'black-box' VSI power circuit. Initially the harmonic performance and the losses associated with the inverter are neglected. The system is also assumed to be operating at steady-state. The basic system is shown schematically in Figure 2.10. When viewed from the a.c. system perspective the ASVC appears as a voltage source, coupled to the line voltage through a small reactance (usually the per-phase leakage inductance of a transformer), which produces fundamental and harmonic voltages. For the following analysis, harmonics are neglected and the ASVC is seen as a pure voltage source.

A purely reactive power flow exists if the inverter output voltages are controlled to produce a balanced 3-phase output in phase with the a.c. system voltage. Due to the inherent characteristics of the coupling components used to connect the ASVC to the a.c. system, the line current flowing into or out of the VSI is ideally 90° to the system voltage.

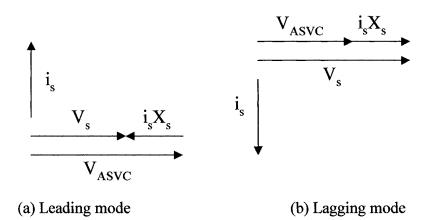

Figure 2.10- Schematic diagram of VSI based ASVC

Under steady-state conditions the ASVC absorbs a leading reactive current if the inverter output voltage amplitude ( $V_{ASVC}$ ) is larger than the a.c. supply voltage ( $V_s$ ). This is illustrated with the phasor diagram shown in Figure 2.11(a). This mode of operation is known as the leading reactive compensation mode. If the inverter output voltage is less than the a.c. supply voltage then a lagging reactive current is drawn from the a.c. power system, as illustrated in Figure 2.11(b). This mode of operation is known as the lagging reactive compensation mode. If the amplitude of the inverter output voltage is equal to the a.c. system voltage then, ideally, the reactive power exchange is zero and the ASVC is considered in a floating state.

Figure 2.11 - VSI based ASVC Steady-State Phasor Diagrams

The amount of reactive power exchange between the ASVC and the system, in both modes of operation can therefore be adjusted by controlling the magnitude of the ASVC output voltage. Because there is no real power exchange,  $I_S$  is a purely reactive current and the reactive power exchanged by the ASVC can be given by:

$$Q = \frac{1 - \frac{V_{ASVC}}{V_S}}{X} V_S^2$$

The d.c. side voltage, which may be controlled via the phase angle control of the switching strategy applied, determines the magnitude of the VSI output voltage. It can therefore be stated that the d.c. voltage level,  $V_{dc}$ , determines the quantity of reactive power generated or absorbed by the ASVC.

In a practical system, the assumptions of ideal sinusoidal output and no losses are obviously untrue. If the ASVC were to maintain its output voltages exactly in phase with the a.c. system voltages there would be no real power exchange. Therefore, the d.c. capacitors would not only have to maintain a controlled voltage level for the required reactive power compensation, but also supply the real power for the losses. This would result in the d.c. capacitors discharging over a period of time. Due to this fact a small phase difference ( $\delta$ ) is created, through the VSI modulation scheme, between the ASVC output voltage and the system voltage. This is needed to supply the small amount of real power to compensate for the system losses and also to maintain the d.c. capacitor voltage at the required level for compensation. This phase angle control technique is also how the ASVC is controlled during the transient operation. If the angle ( $\delta$ ) is controlled such that the real power delivered is greater than required for the losses then the d.c. capacitor voltage will rise. Hence, moving the system into the leading mode of operation. Whereas, if the phase angle is controlled such that real power is drawn from the capacitor banks, the voltage will drop and the system will move into the lagging mode of operation. The real power exchange between the system and the ASVC is given by:

$$P = \frac{V_{ASVC}V_S}{X}\sin(\delta)$$

With regards to the ideal sinusoidal output, for a high power ASVC application the implemented switching strategy frequency will be restricted due to power losses. Hence, the output voltage will be a formulation of square waveforms dependant upon the pulse width modulation (PWM) scheme and will therefore contain harmonic components. Resulting from this the total 3-phase instantaneous power will not equate to zero and in order to maintain this equality the inverter will draw a fluctuating current from the d.c. capacitor. The ripple current waveform is typically a function of the harmonic components of the ASVC output voltage. Investigations into the d.c. ripple waveforms and their overall effect of the harmonic performance of the ASVC system will be presented in Chapter 9. It is apparent that the d.c. capacitors not only perform an important role in the ASVC system performance but also a large part of the total system cost. An investigation into the appropriate sizing of the d.c. capacitors is essential for the practical application of the ASVC system.

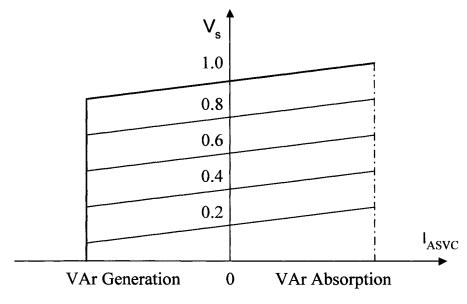

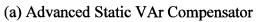

To conclude this introduction into the ASVC, it is worth noting that due to the generation or absorption of reactive power being controlled by the inverter a.c. output voltage, the reactive power output can be controlled independent of the a.c. supply voltage. The reactive current values available from the ASVC are only dependant upon the system rating. Comparing the V-I characteristics of the conventional SVC to the ASVC, shown in Figure 2.12, illustrates the superiority of the ASVC in providing voltage support [11]. This results from the reactive current of the conventional SVC being directly proportional to the a.c. system voltage.

(b) Static VAr Compensator

Figure 2.12 – V-I Characteristics for the ASVC and SVC

# **3 SHUNT STATIC VAR SYSTEM (SVS) TOPOLOGIES**

#### 3.1 INTRODUCTION

When investigating FACTS shunt compensation technology, it is important to have a general understanding of the options available for the various circuit topologies. Therefore, it is necessary to have an understanding of the past, present and future power semiconductor options together with the  $1^{st}$  and  $2^{nd}$  generation of available power circuit concepts and topologies for FACTS VAr compensators.

This Chapter presents an overview of the available power semiconductor devices and typical topologies implemented in the 1<sup>st</sup> and 2<sup>nd</sup> generation shunt FACTS VAr compensators. The SVC and ASVC are presented with characteristics of operation, comparative analysis and reference to industrial application.

#### 3.2 POWER ELECTRONIC DEVICES USED IN SHUNT VAR COMPENSATORS

FACTS technology using thyristor based equipment to improve the utilisation and quality of a.c. networks have been implemented effectively now for many years. More recently equipment requiring fully controllable power electronic devices have emerged at various installations. The advances in power semiconductor devices heavily effect the development of this equipment [19]. In general, power electronic devices can be separated into three groups:

- Uncontrolled such as a power diode.

- Semi-controlled also referred to as latching devices, these are turned on via the gate but require circuit commutation in order to extinguish current flow.

- Fully controlled with these devices the current flow can be both initiated and extinguished by gate control.

Although power diodes are not controllable, they play a very important role in improving the performance of the switching devices used in the power circuitry. They provide a freewheeling element to power devices used in converter applications, such as GTO's and IGBT's. Conventional converter grade diodes have been found to be too slow for these applications and this has resulted in the emergence of fast recovery diodes.

The semi-controlled thyristors are often referred to as the 'workhorse' of the power electronics business. Utilised in series and parallel to increase power ratings, thyristors have been used throughout shunt compensation systems such as the TCR and TSC schemes for many years. The conventional thyristor has been the device of choice for almost all HVDC projects, some FACTS controllers, and a large number of industrial applications [4]. The 2<sup>nd</sup> generation FACTS VAr compensators require the switching elements to have turn-off capabilities so that the converter can both generate and absorb reactive power. Examples of high power semiconductor devices with a fully controlled capability that are suitable for the FACTS VAr compensators include:

- Gate Turn-Off (GTO) Thyristor high power (5-8 kV)

- Insulated Gate Bipolar Transistor (IGBT) –low to medium power (3-5 kV)

- Integrated Gate Commutated Thyristor IGCT high power (state-of-theart / future)

The phase limbs of a converter are an assembly of valves and each valve is an assembly of power devices. Several schemes have been implemented to generate controllable reactive power by using various power electronic switching converters and there are several reports conducting comparative analysis of the devices [9,11,19,20,21]. The results have indicated that it is favourable to utilise the GTO, IGBT and more recently the IGCT.

The main factors influencing the selection of a power device can be ultimately reduced to a compromise between performance and overall cost. Utilising devices with the highest possible current and voltage ratings should be considered but the apparent advantage of requiring fewer devices can be outweighed by disproportionately higher device and auxiliary component costs, poorer dynamic performance or higher losses. A cost comparison of power electronic systems using GTO's and IGBT's was carried out by Lorenz [20] and shows a big margin in favour of IGBT's.

The GTO thyristor is still the present choice for industrial high power FACTS equipment requiring fully controllable devices, despite its complicated gate drive and snubber circuits. The device enables high current turn-off capabilities with high voltage blocking ratings and, subject to selection for matched characteristics and attention to equipment design, it can be used in series strings. These factors have recently been improved with the development of the IGCT. The application of the GTO is usually limited to low frequency, typically below 1 kHz, due to the high switching losses associated with the device.

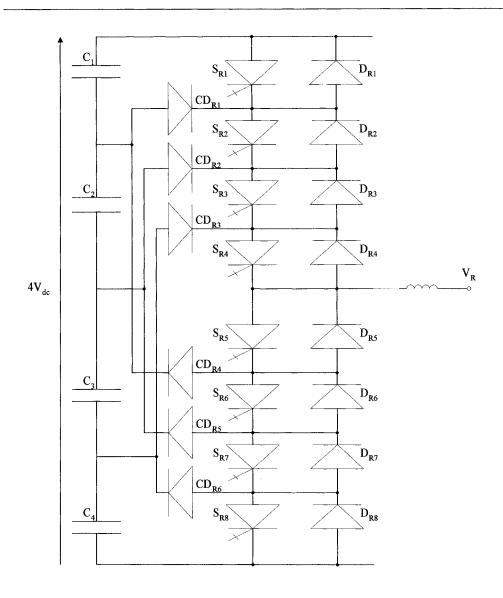

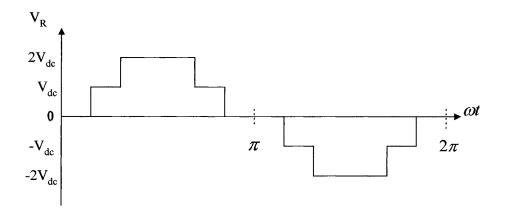

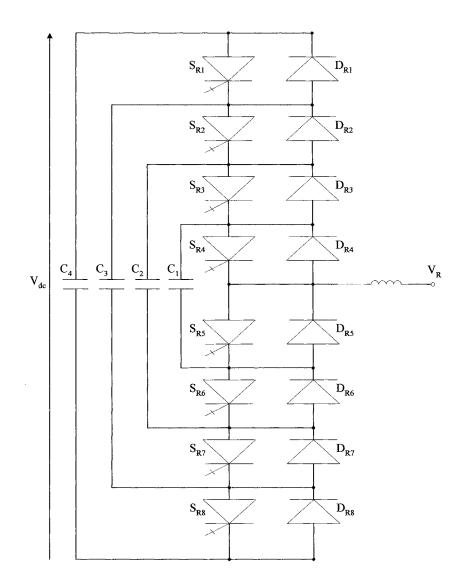

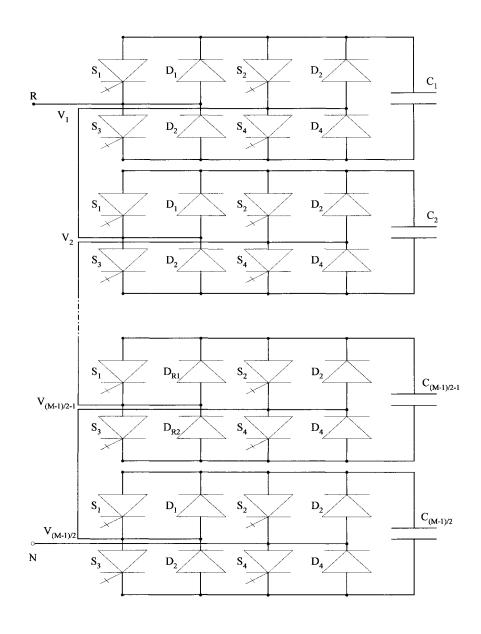

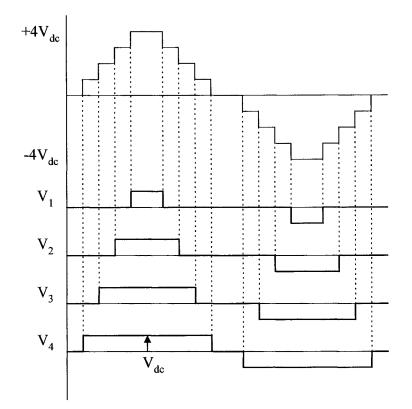

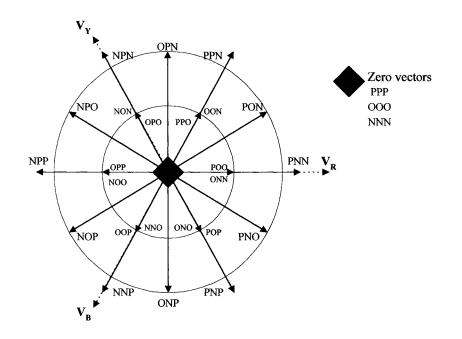

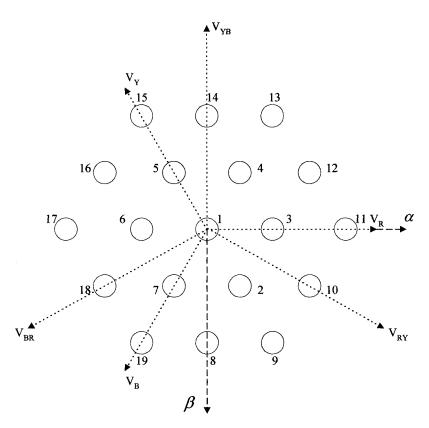

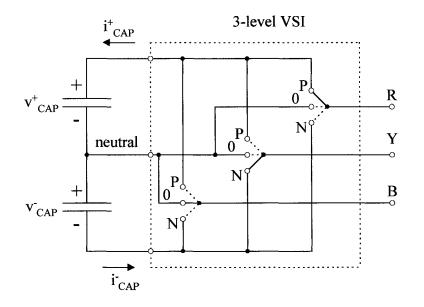

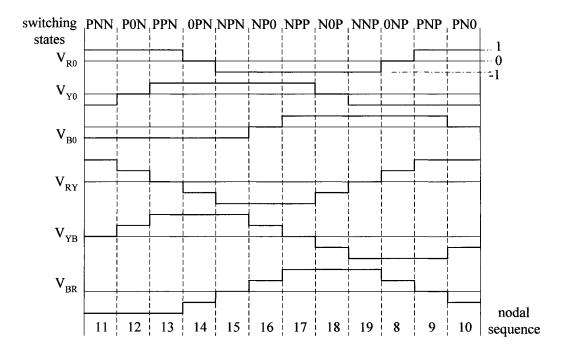

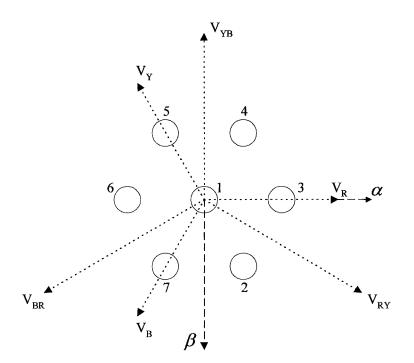

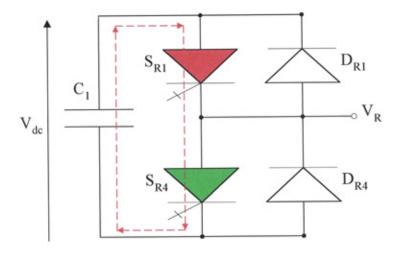

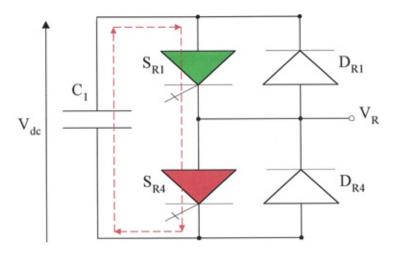

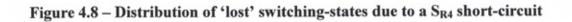

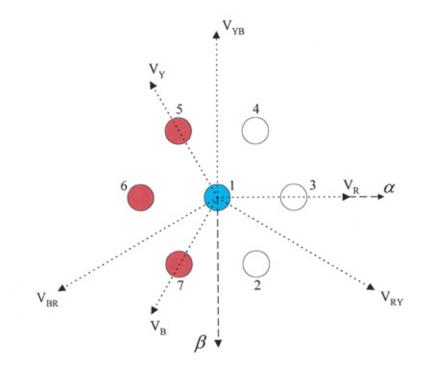

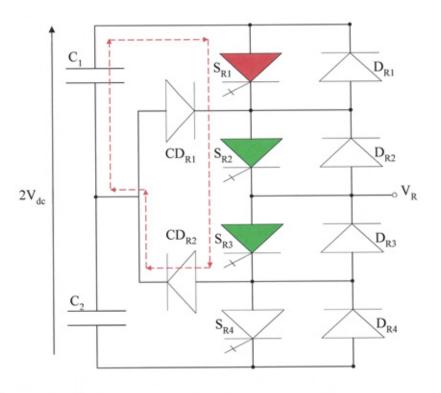

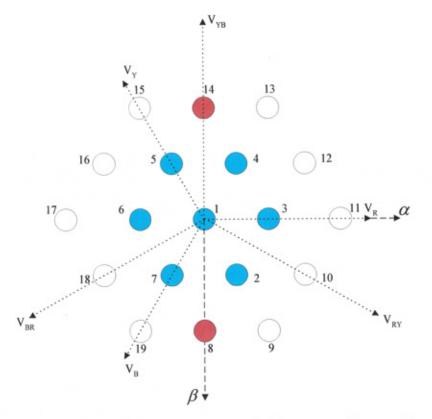

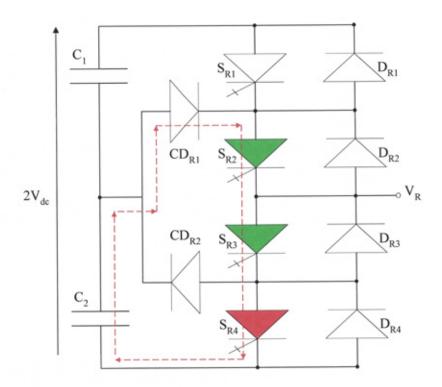

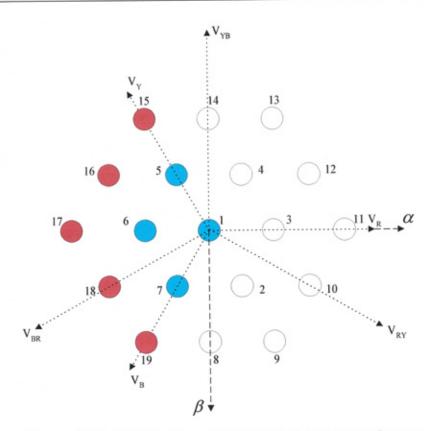

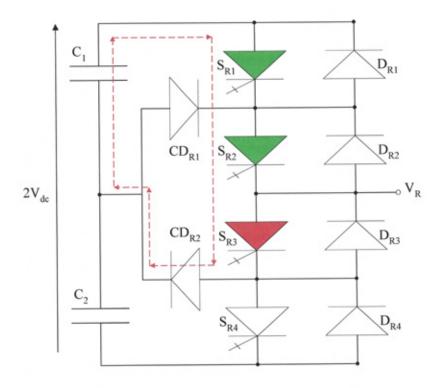

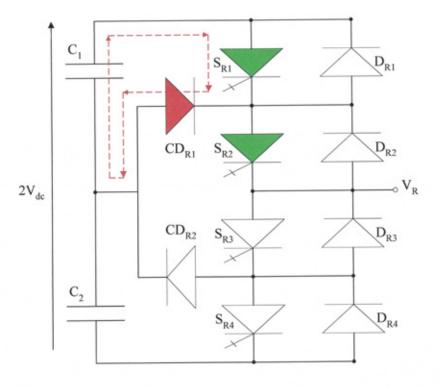

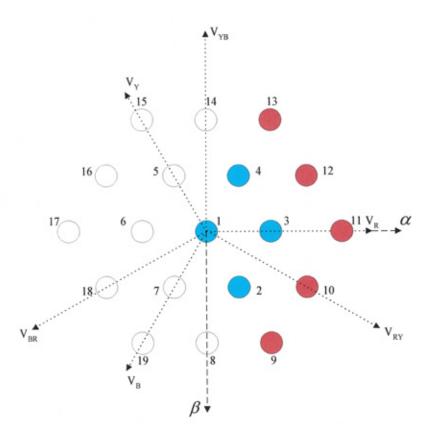

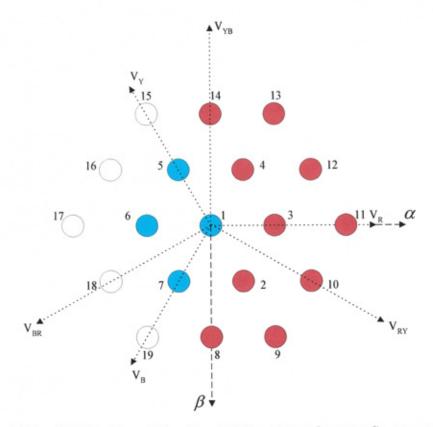

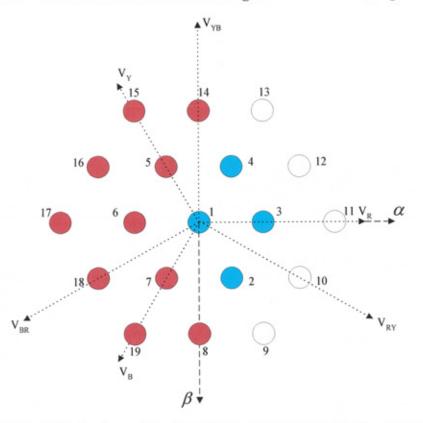

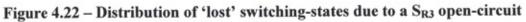

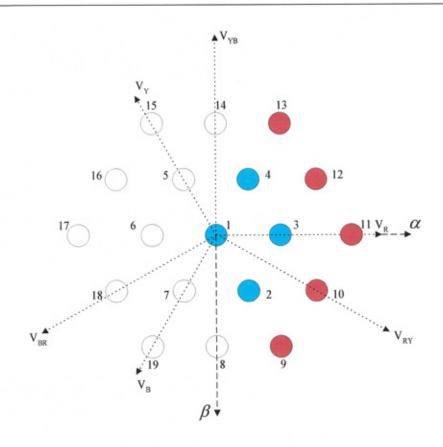

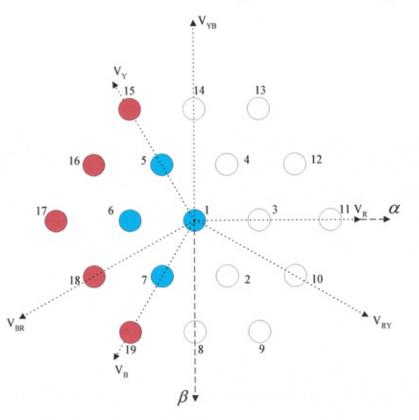

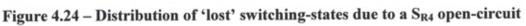

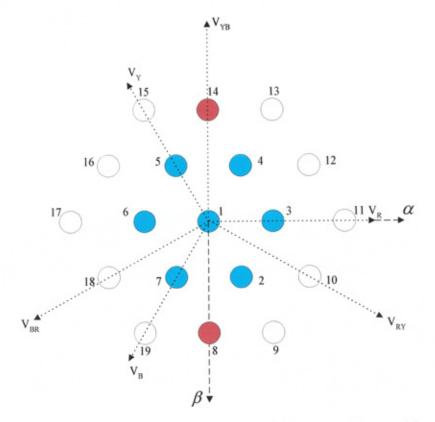

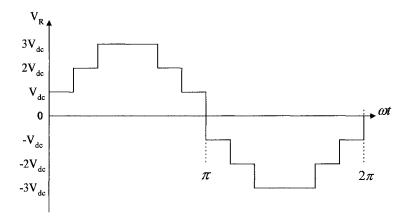

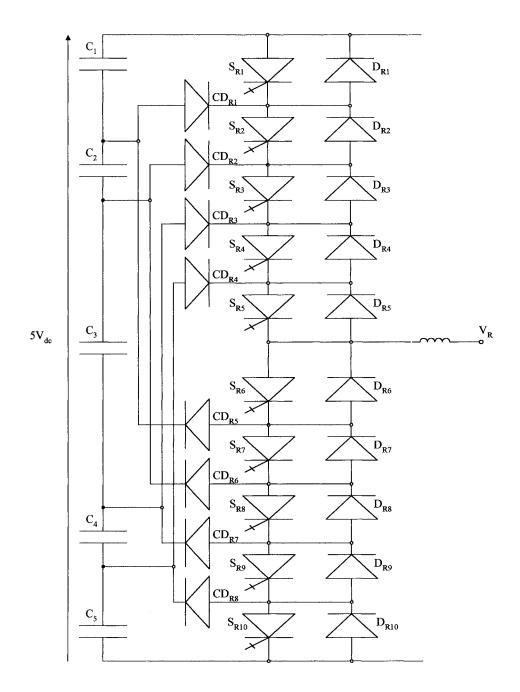

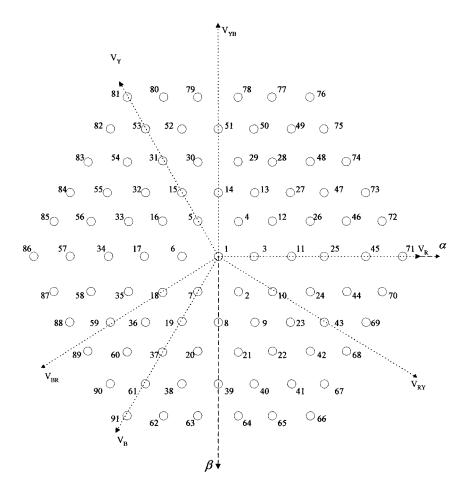

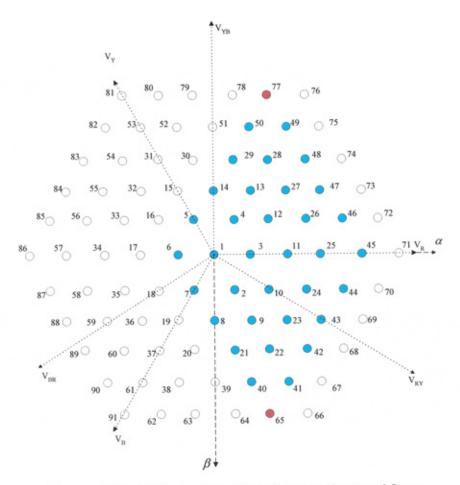

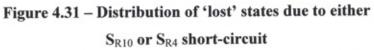

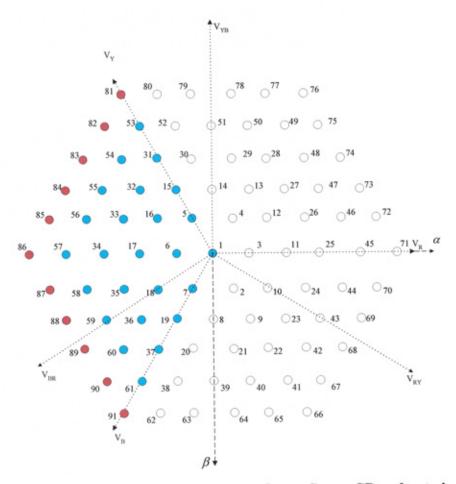

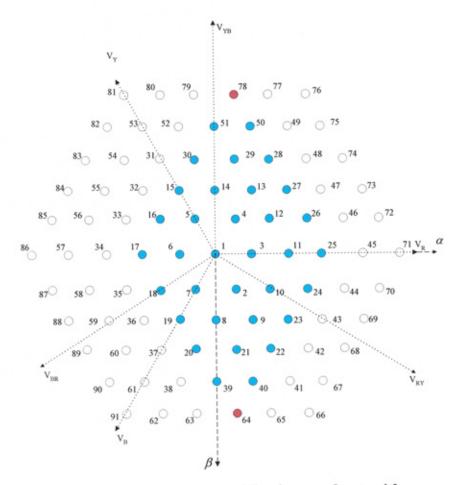

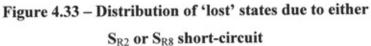

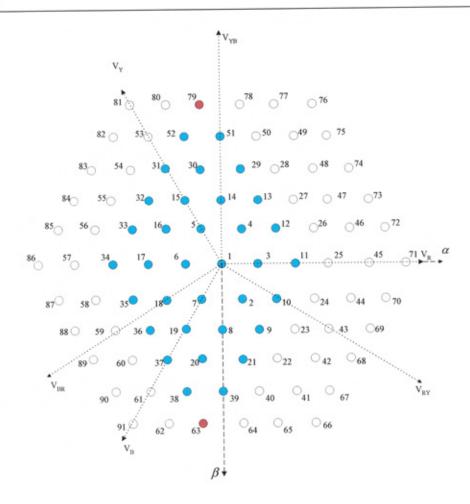

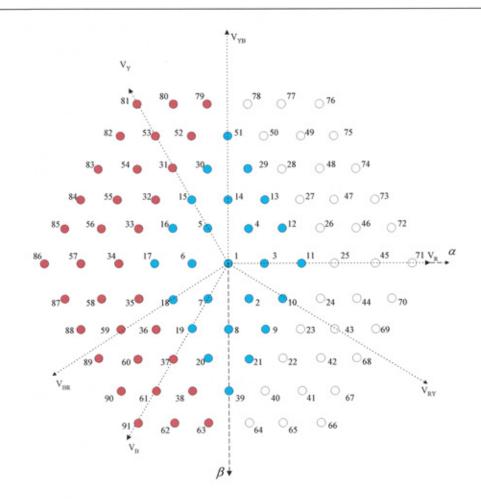

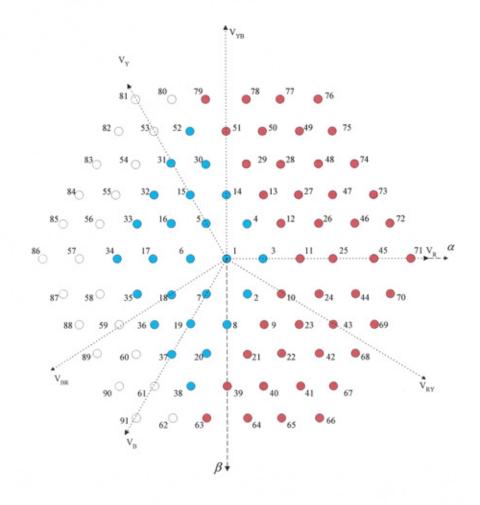

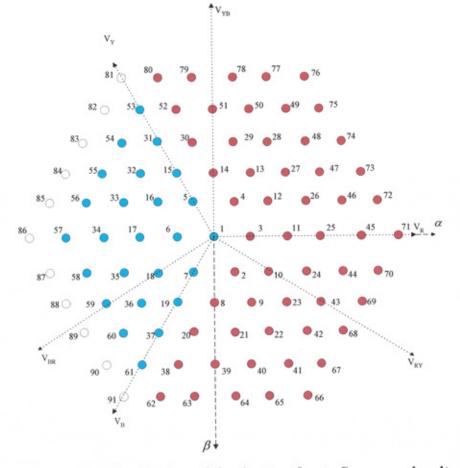

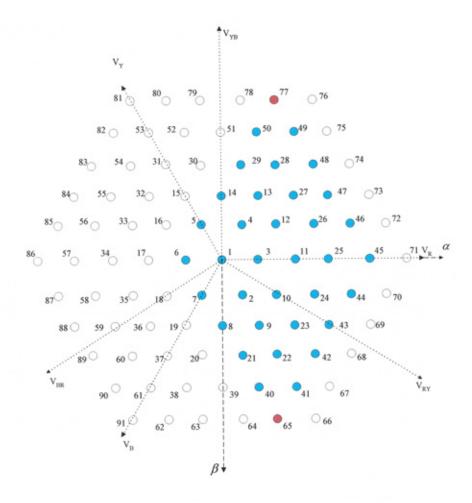

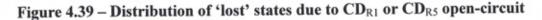

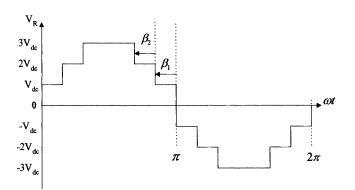

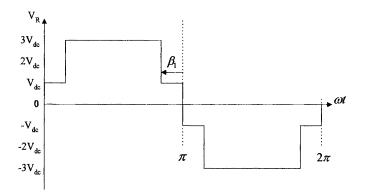

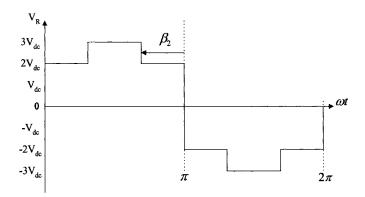

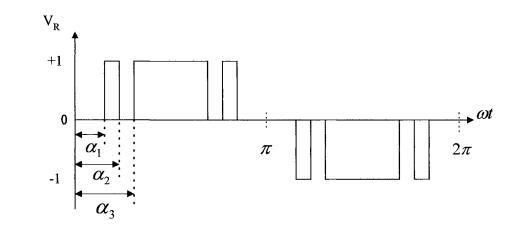

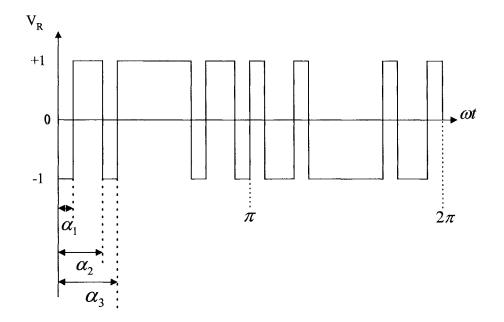

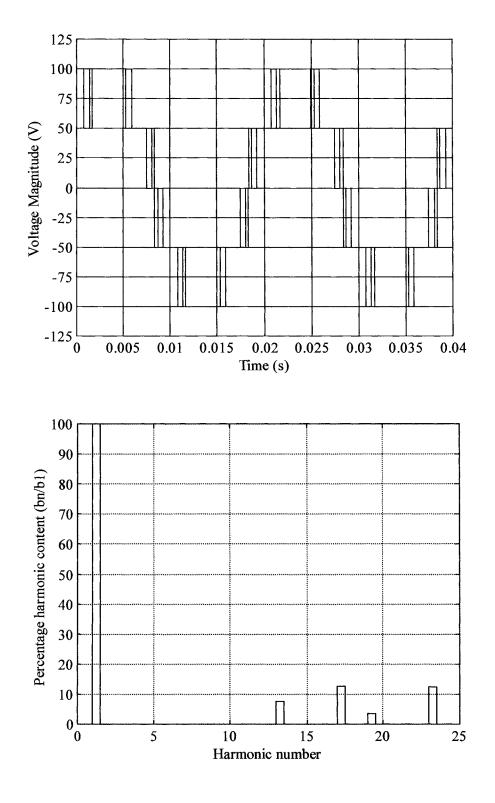

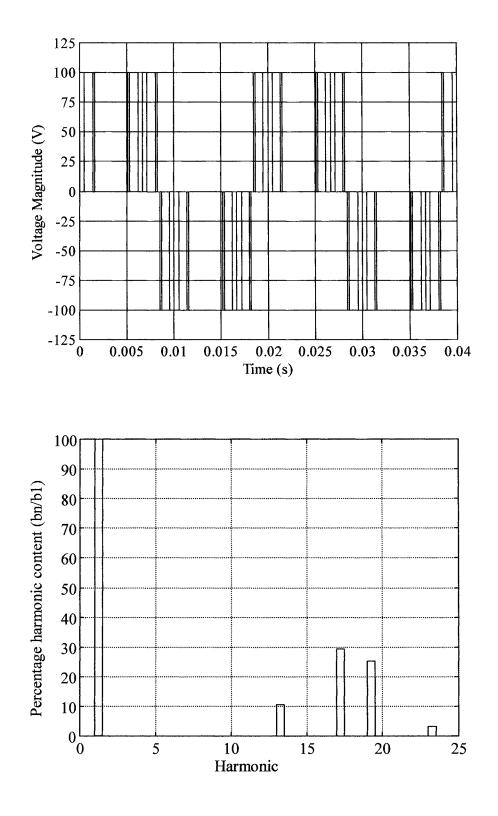

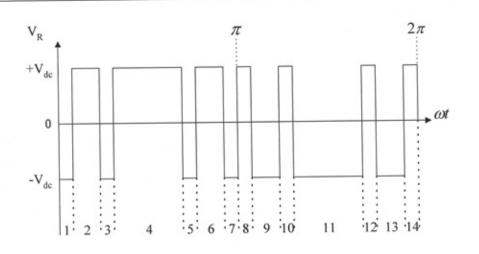

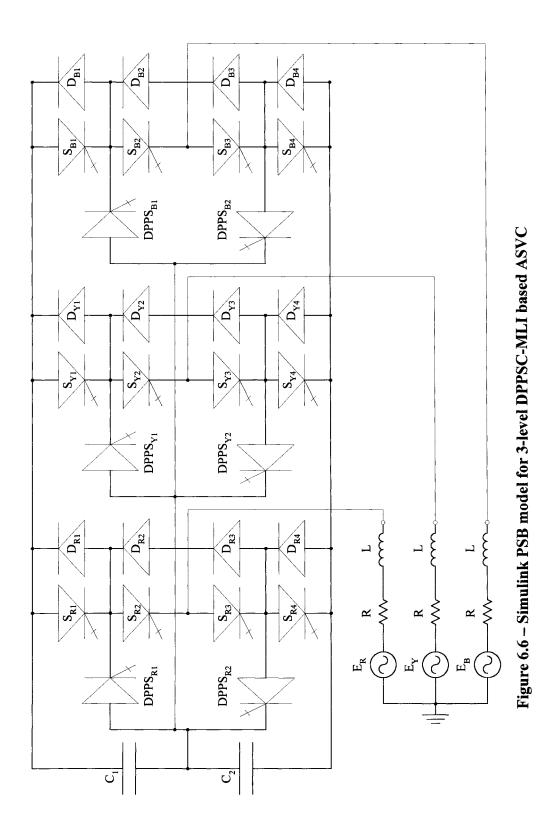

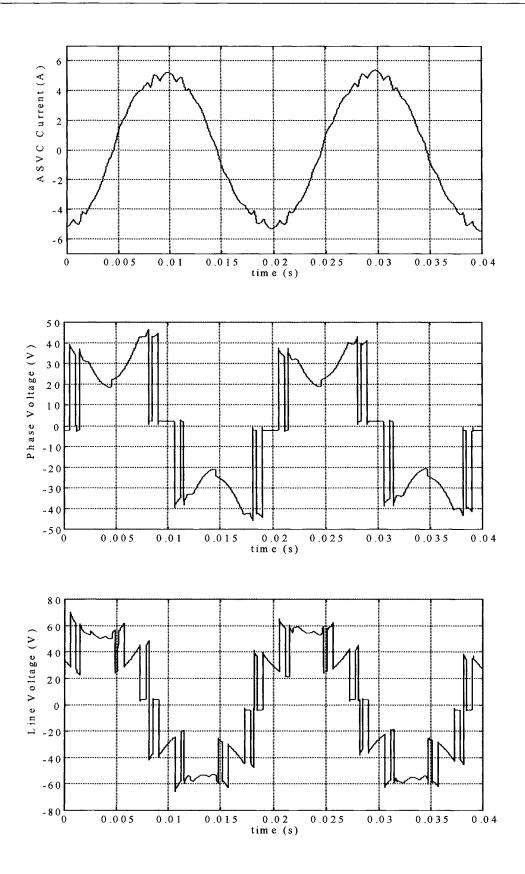

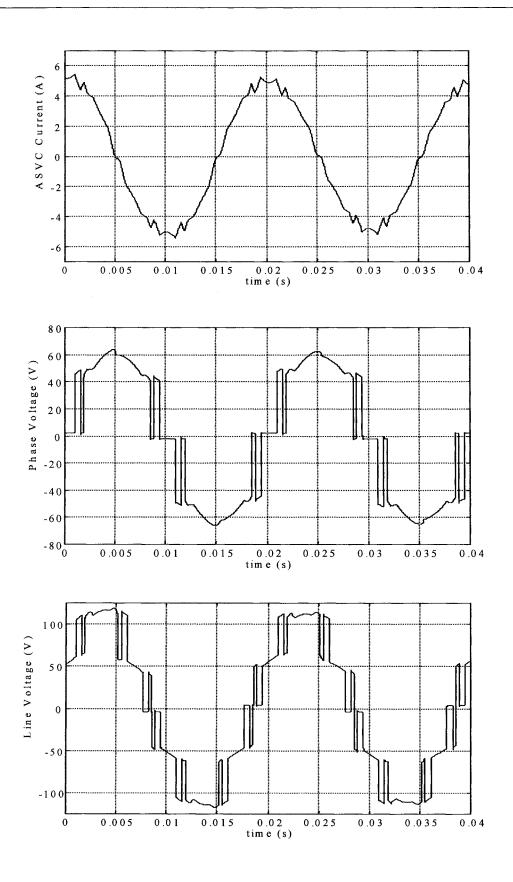

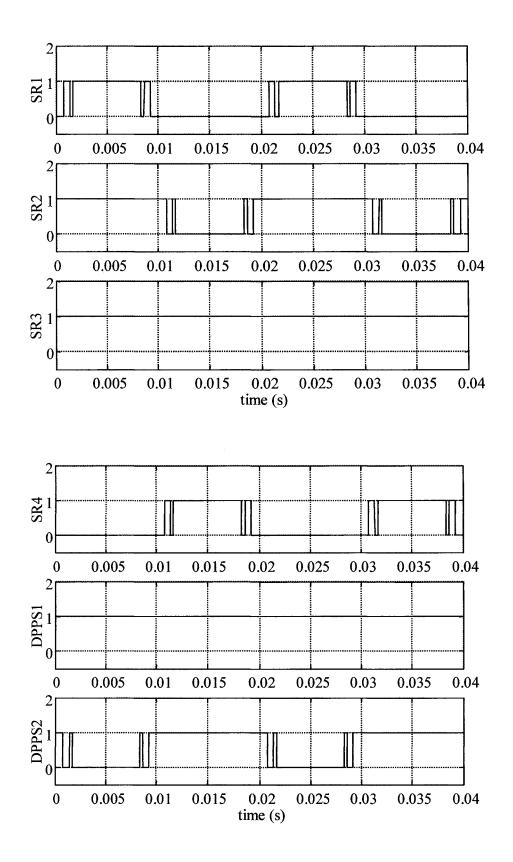

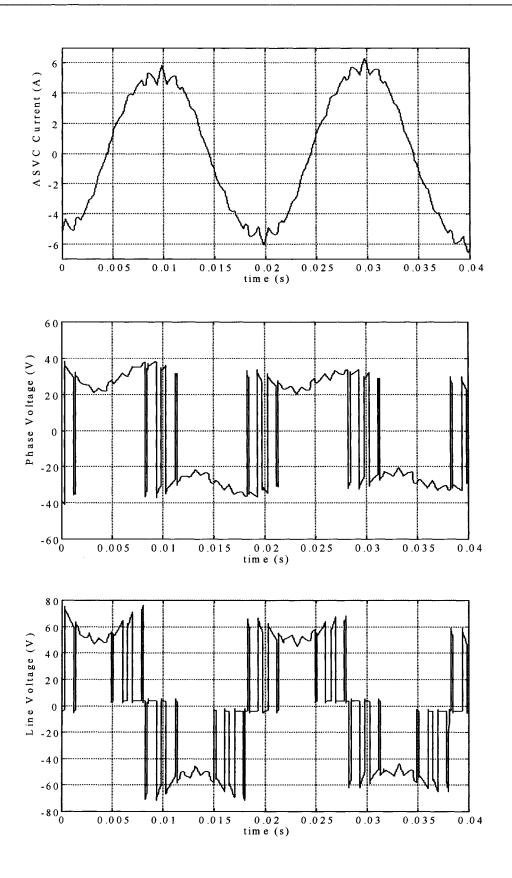

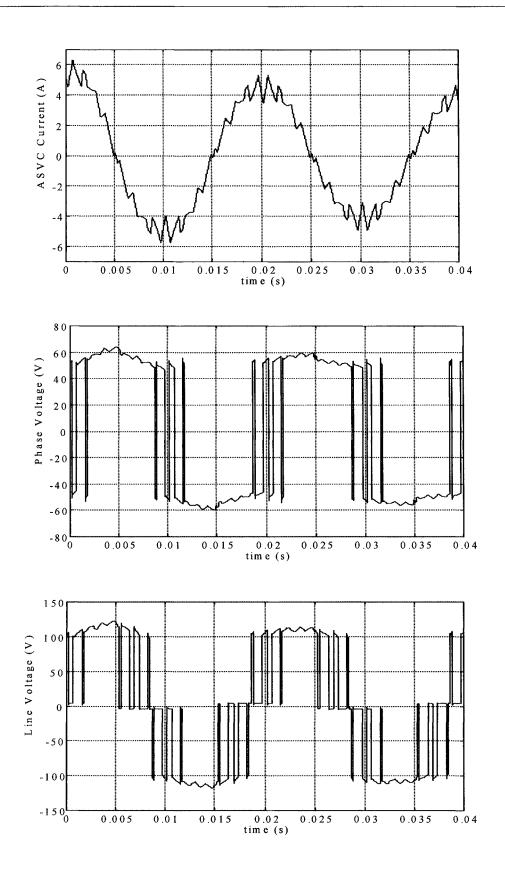

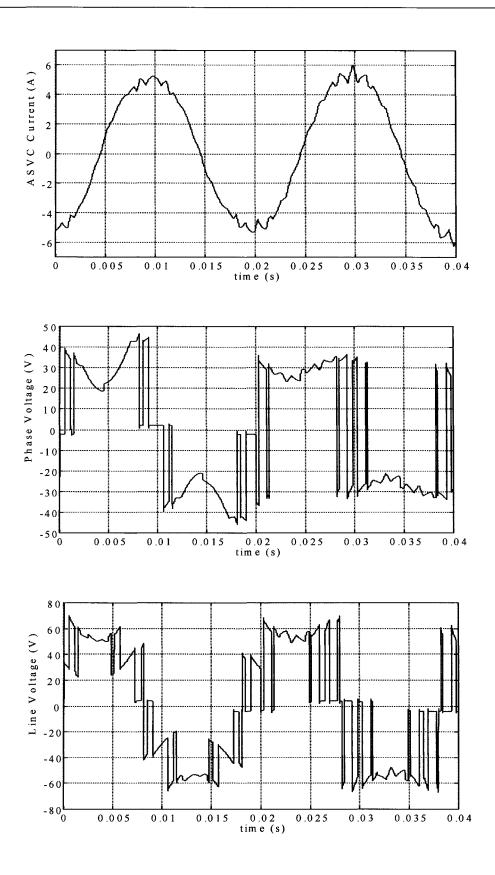

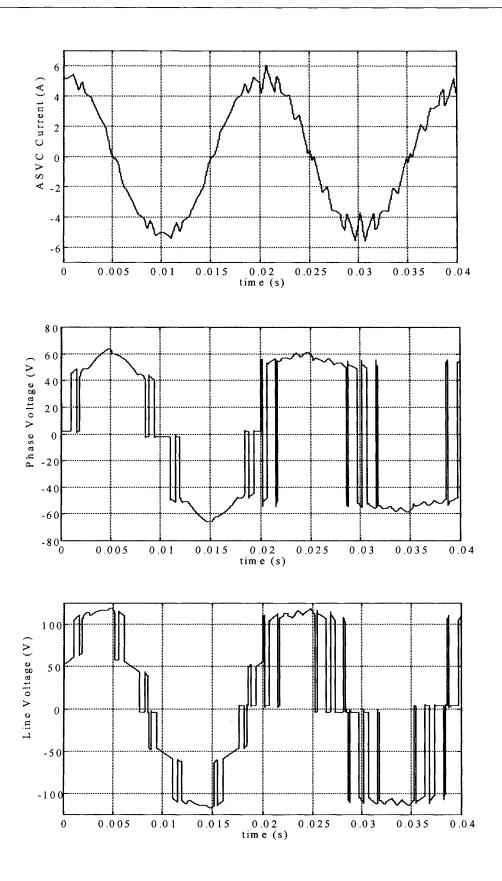

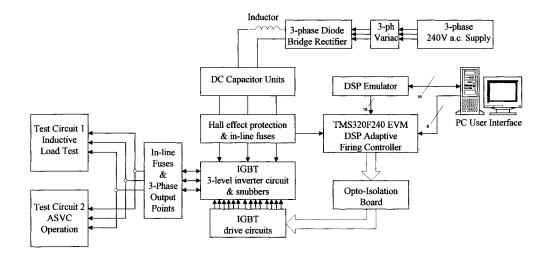

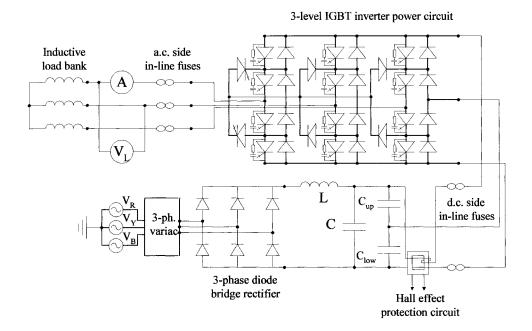

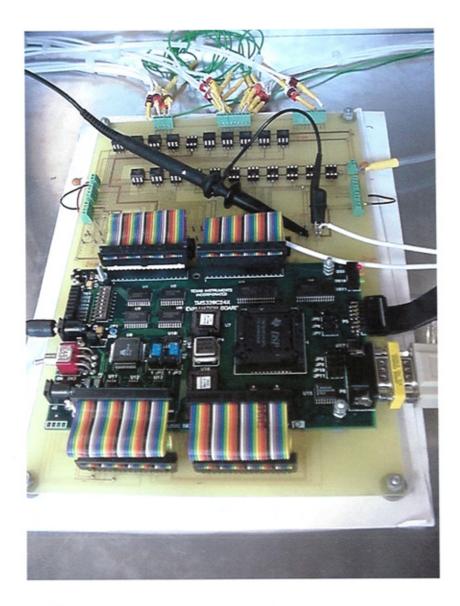

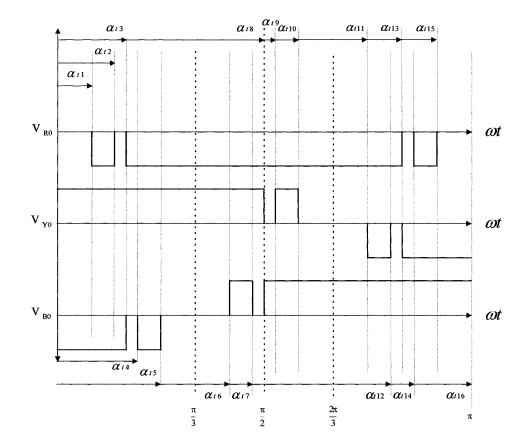

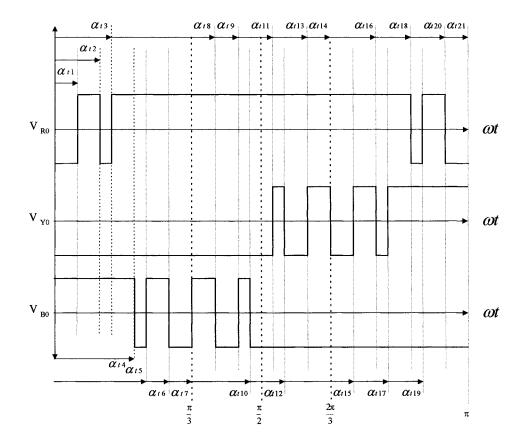

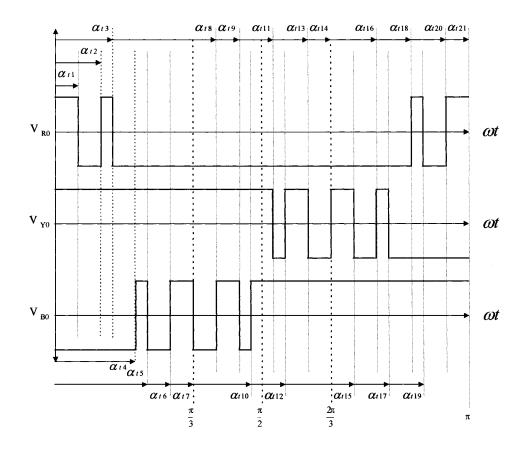

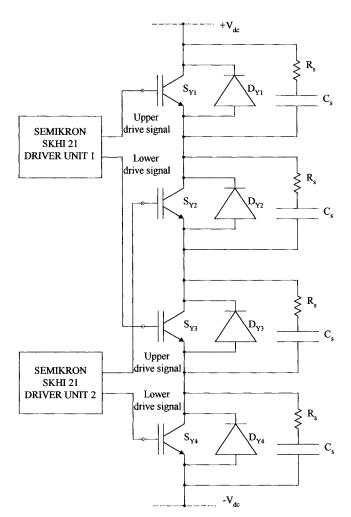

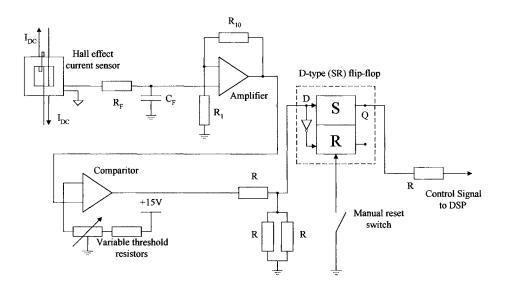

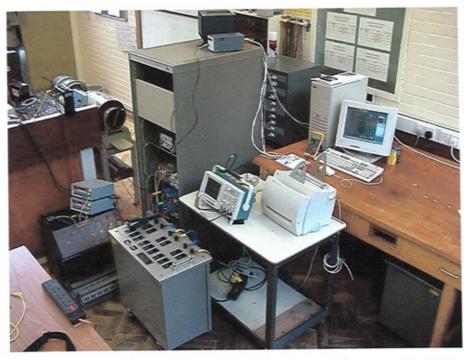

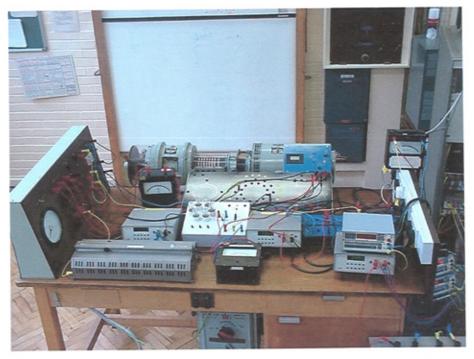

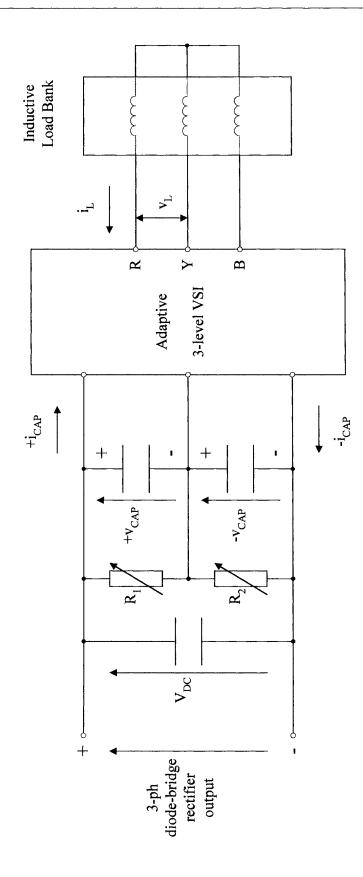

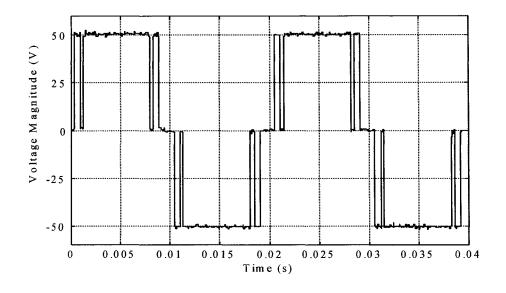

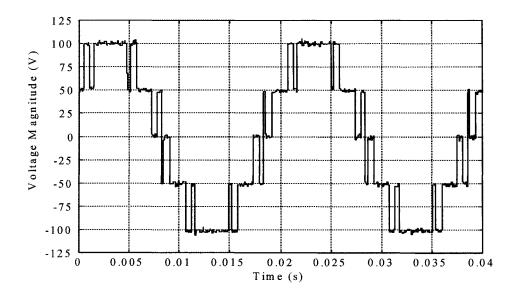

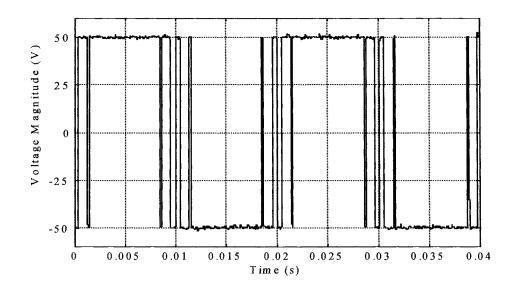

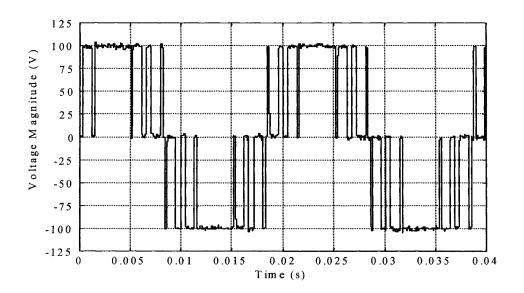

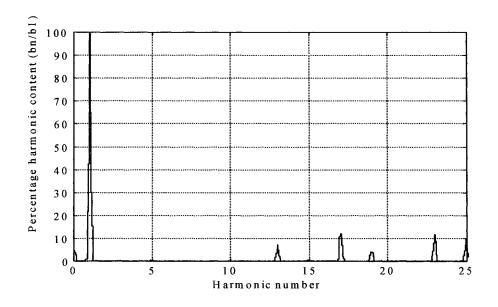

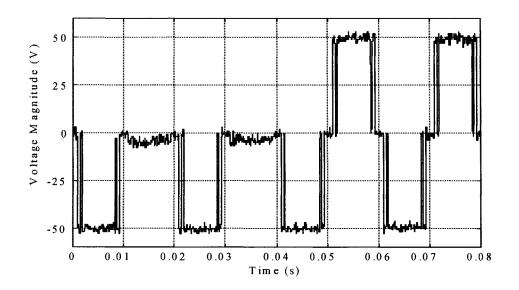

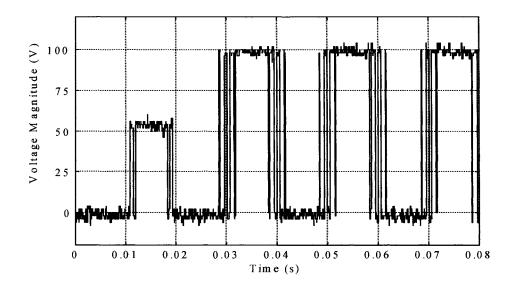

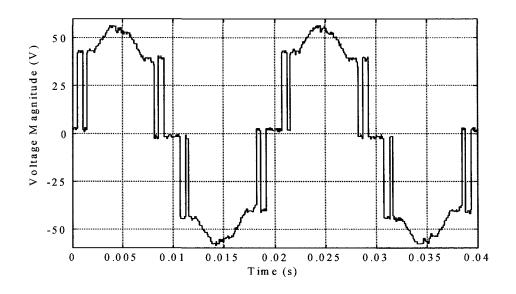

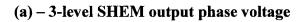

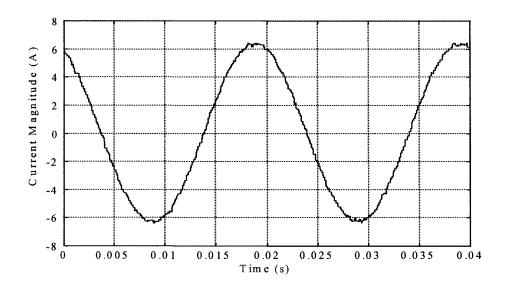

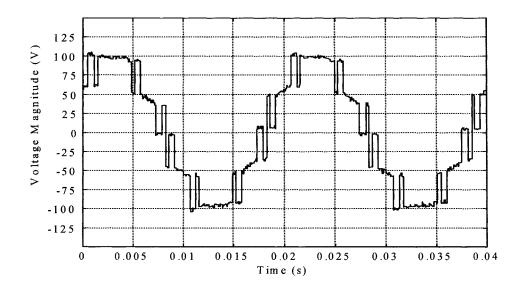

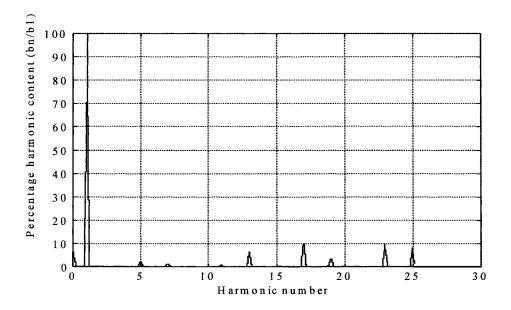

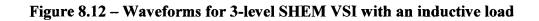

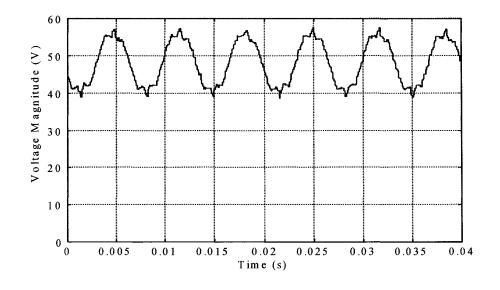

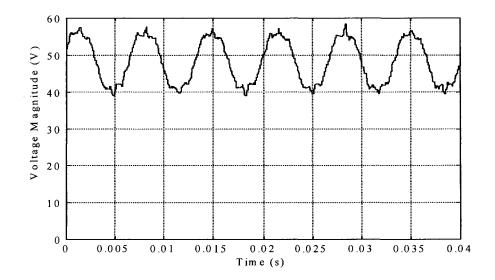

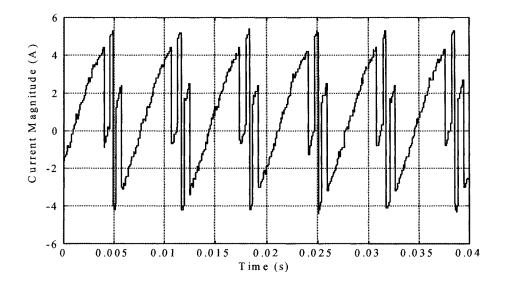

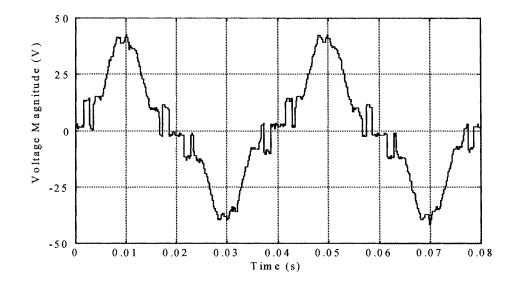

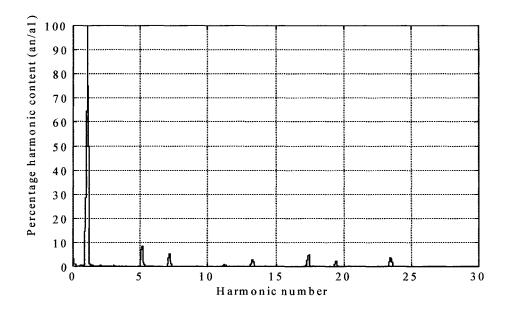

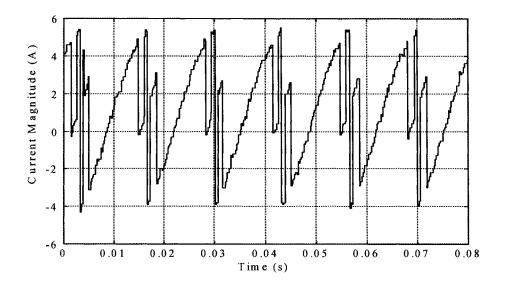

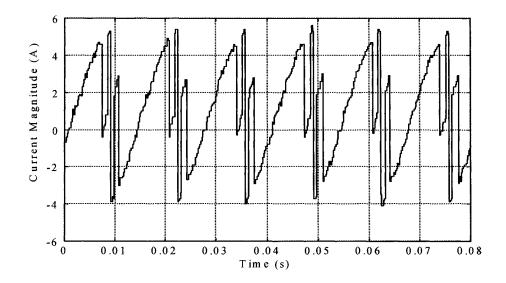

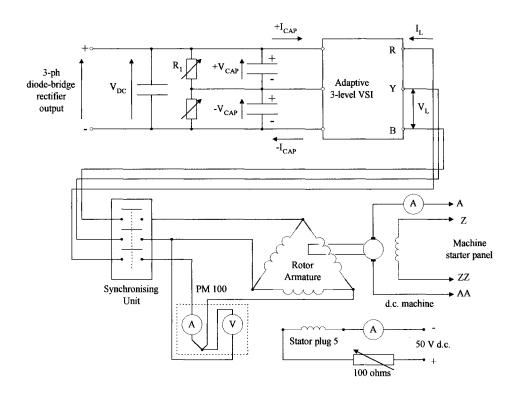

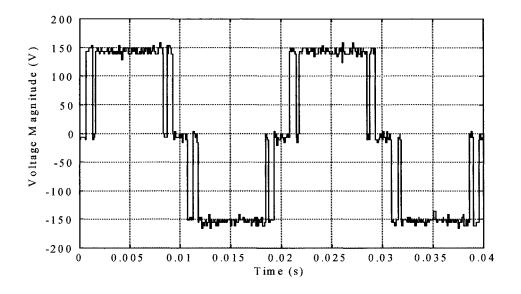

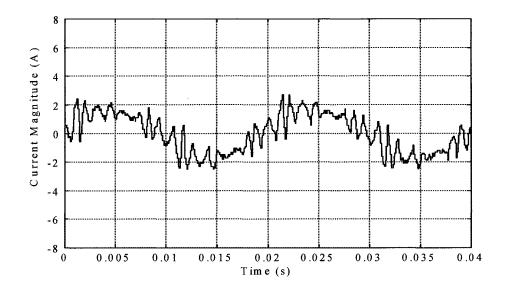

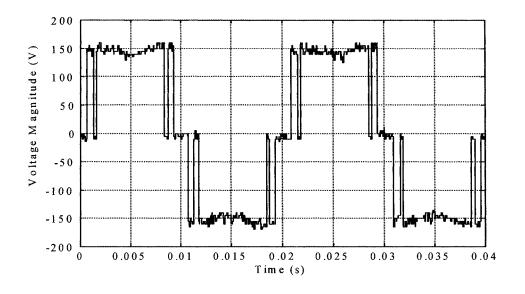

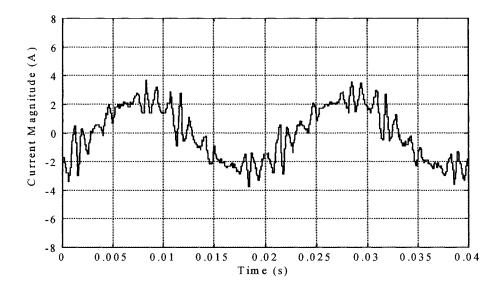

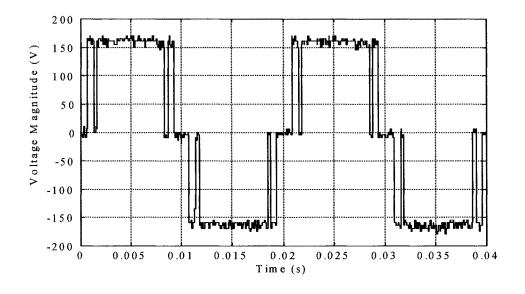

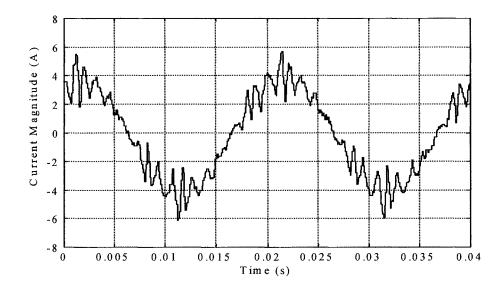

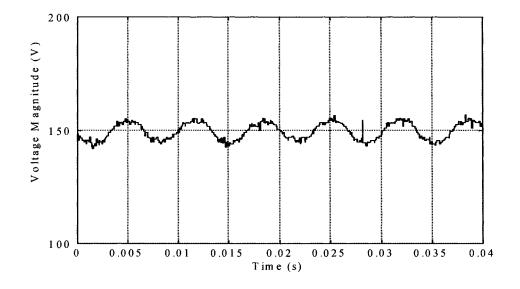

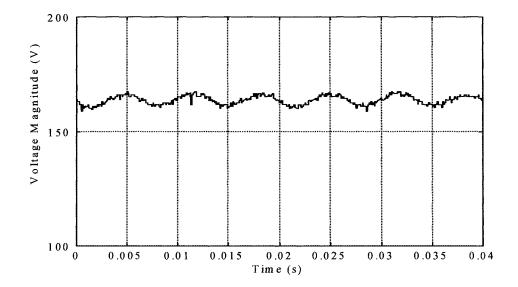

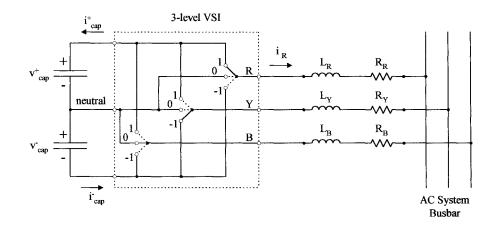

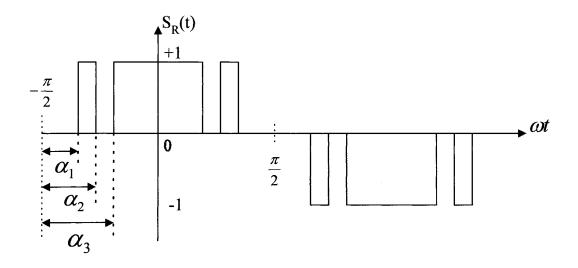

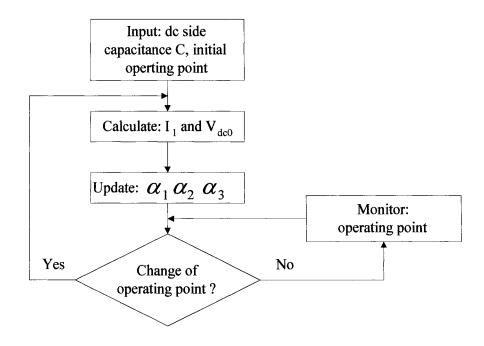

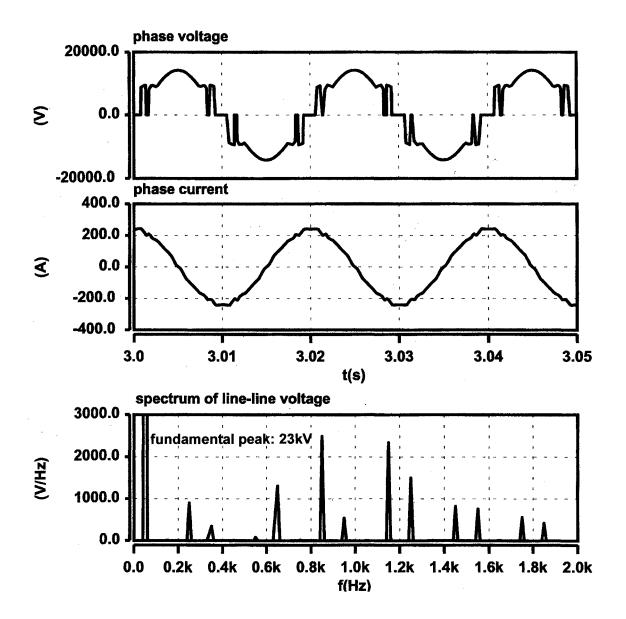

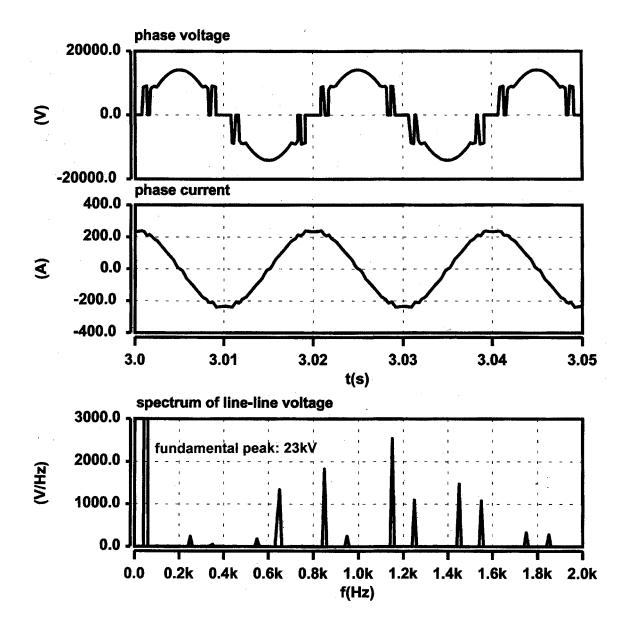

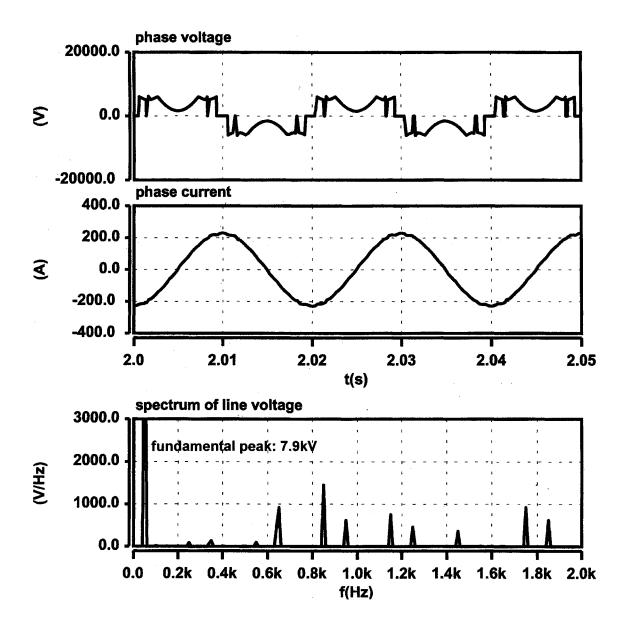

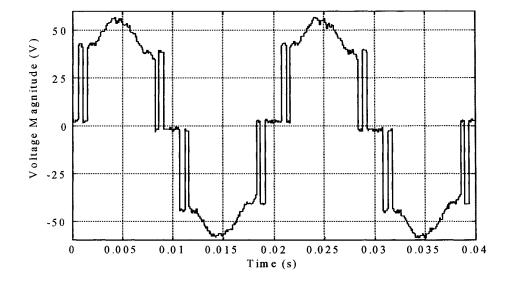

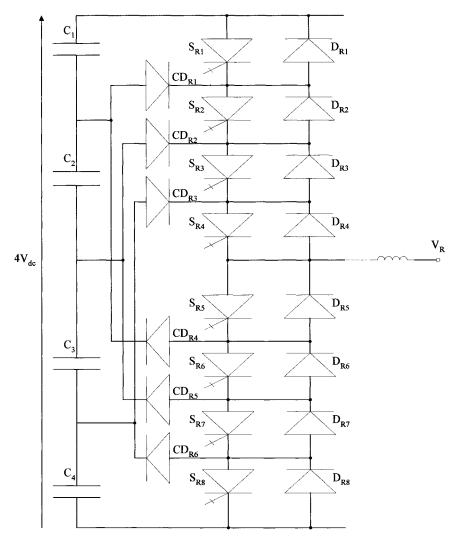

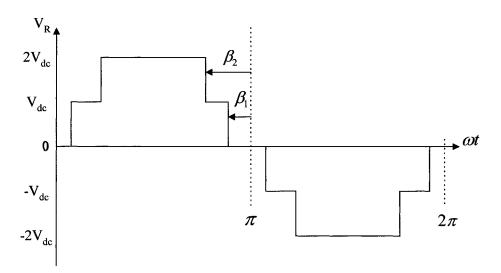

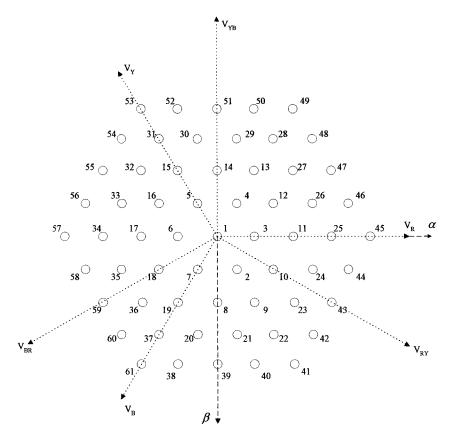

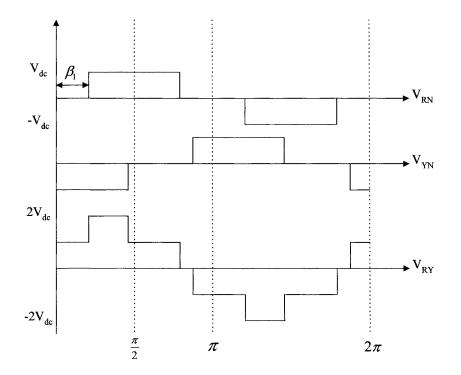

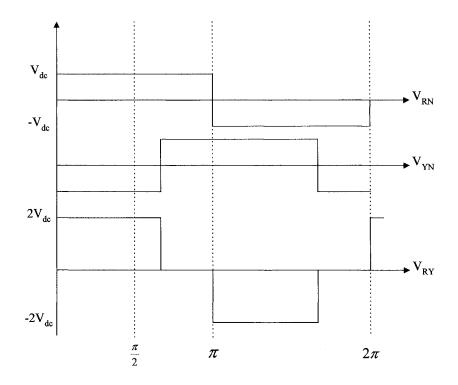

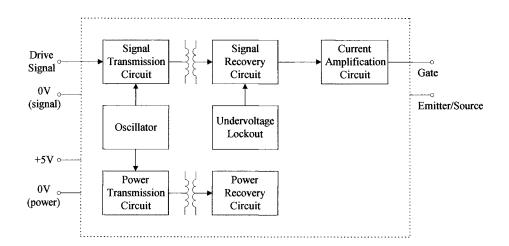

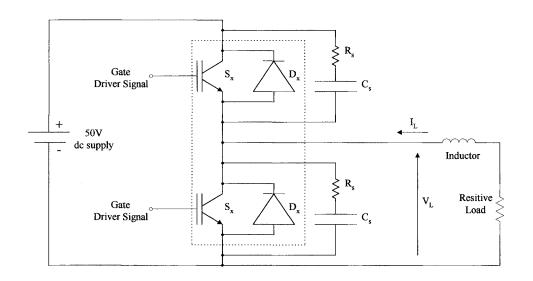

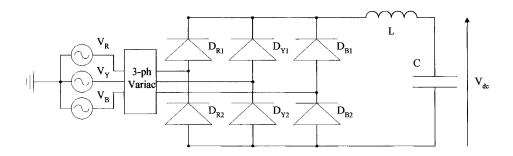

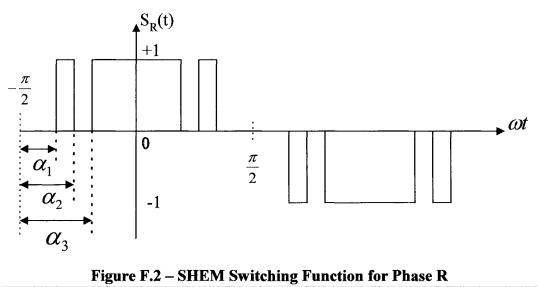

As this project investigates the inherent redundancy of a converter topology in the event of a device fault it is also worth noting that the device selection must consider possible fault scenarios to predict current and voltage margins and the requirement for possible device redundancy. In general, power devices fail short circuit enabling continual operation at a valve if the topology, control scheme and remaining device ratings are suitable.